DS734 September 16, 2009

**Product Specification**

# Introduction

The XPS USB Host Controller is a soft Xilinx IP core for use with the Xilinx Embedded Development Kit (EDK). The core is designed to support the Enhanced Host Controller Interface (EHCI) for USB 2.0 host controllers. The core incorporates integral DMA function controlled by the EHCI Controller block. This assures the highest performance data transfer topology with the system memory. The Standard EHCI register set is accessed via a PLBV46 Slave interface, affording support by the Xilinx MicroBlaze<sup>TM</sup>, Power<sup>®</sup>PC 405, and PowerPC 440 microprocessors. The core interfaces to an external USB 2.0 PHY (physical interface) via the industry standard ULPI signal interface (8-bit data).

# Features

- USB 2.0 Host Controller (v1\_01\_a)

- USB High speed device support (480 Mbps)

- USB Full Speed device support (12 Mbps)

- Low speed devices are not supported

- Supports Intel EHCI 1.0 specification for standardized register and system software (RTOS) interfaces

- Integrated Transaction Translator enables the use of EHCI RTOS interface for Full Speed device support

- OHCI and UHCI RTOS support is not required

- Incorporates ULPI PHY (8-bit data) interface for external (to FPGA) USB 2.0 PHY connection per ULPI v1.1 specification

| LogiCORE™ IP Facts             |                                                                                    |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------|--|--|--|

| C                              | ore Specifics                                                                      |  |  |  |

| Supported Device<br>Family     | Virtex <sup>®</sup> -6, Virtex-5, Virtex-4,<br>Spartan <sup>®</sup> -6, Spartan-3A |  |  |  |

| Resources Used                 | See Table 21, Table 22, Table 23                                                   |  |  |  |

| Version of core                | 1.01a                                                                              |  |  |  |

| Prov                           | vided with Core                                                                    |  |  |  |

| Documentation                  | Product Specification                                                              |  |  |  |

| Design File Formats            | VHDL                                                                               |  |  |  |

| Constraints File               | EDK TCL Generated                                                                  |  |  |  |

| Verification                   | N/A                                                                                |  |  |  |

| Instantiation Template         | EDK                                                                                |  |  |  |

| Design                         | Tool Requirements                                                                  |  |  |  |

| Xilinx Implementation<br>Tools | ISE® 11x                                                                           |  |  |  |

| Verification                   | ModelSim PE/SE 6.4b or later                                                       |  |  |  |

| Simulation                     | ModelSim PE/SE 6.4b or later                                                       |  |  |  |

| Synthesis                      | XST                                                                                |  |  |  |

|                                | Support                                                                            |  |  |  |

| Provided by Xilinx, Inc.       |                                                                                    |  |  |  |

© 2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

www.xilinx.com

# Features (contd)

- USB 2.0 Host Controller (v1\_01\_a)

- Integrated DMA functionality for efficient data transfers between the Host Controller and System memory

- PLBV46 Master interface provided for dedicated DMA of USB data and EHCI transfer descriptors to and from the Embedded System main memory

- DMA functionality is leveraged from the EHCI defined functionality and is autonomous to the Embedded System software

- PLBV46 Slave interface for register access and configuration by the Embedded System microprocessor

# **Functional Description**

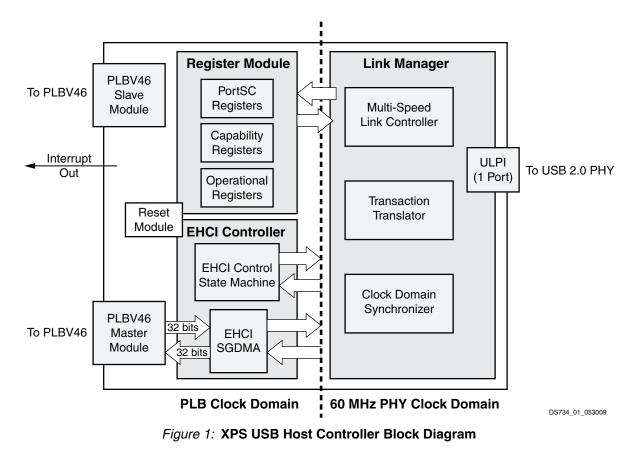

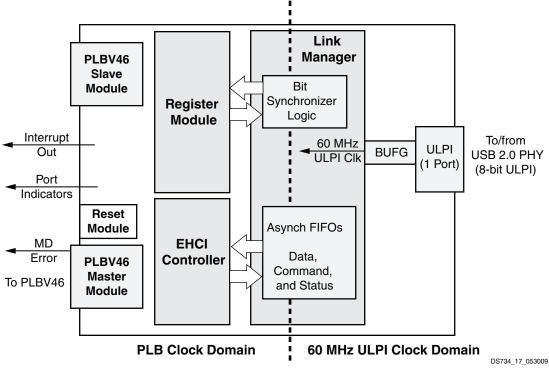

Figure 1 illustrates the functional composition of the core. The design is an Xilinx Pay Core and delivered using the Xilinx EDK tool suite. Pay Cores are delivered in EDK as encrypted source files and contain a disable timer. Purchasing the appropriate Xilinx core license will enable the delivery of the core without the disable timer. The core may be used in evaluation mode which allows for approximately 8 hours of operation before being disabled.

The core's design has three primary interfaces, the PLBV46 Slave interface, the PLBV46 Master interface, and the 8-bit ULPI interface. Register access and configuration is provided via the PLBV46 Slave interface. High speed DMA connection to system memory is via the PLBV46 Master interface. The backend connection to an external USB 2.0 PHY is provided with the ULPI interface (8-bit data).

The register interface for the Host Controller is provided by the Register Module. The standard EHCI Specified register set includes the Capability Registers, the Operational Registers, and one PortSC register (single port root hub emulation). In addition, the Linux programming model for use with a Transaction Translator requires an additional non-EHCI R/W register designated the Mode Register. A single system interrupt is generated within the Register Module and is output for routing to the User's System Interrupt Controller. The interrupt is a merged (OR) of the operational interrupts required by the EHCI specification. The Register Module also generates the Port Indicator. These are provided for use by the User to connect to external port indicator LEDs and reflect the EHCI port indicator bit definitions (See the PORTSC register). The Host Controller's Register compliment is detailed in "XPS USB Host Registers".

The EHCI Controller Module is the main control logic for supporting the EHCI Transfer Descriptor (TD) execution and system interface protocol. It also controls the DMA operations for TD fetch and store as well as the USB Data fetch and store with the Embedded System Main Memory. This is via the Host's PLBv46 Master interface.

The Link Manager (LM) is responsible for management of the external USB 2.0 PHY via the ULPI interface. The LM includes 3 major sub-blocks, the Multi-Speed Link Controller (MLC), the Transaction Translator (TT), and the Clock Domain Synchronizer. The MLC is responsible for management of the ULPI interface and the external USB 2.0 PHY. This includes device connect/disconnect detection, speed evaluation, port power management, suspend/resume, and port reset control. The Transaction Translator is active when a Full Speed device is connected directly to the Host Controller's single root hub port. The TT provides the necessary logic and buffering to translate Hi-speed EHCI controlled protocol to Full Speed protocol. The TT is not active if a Full Speed device is connected to the Host via an external HS Hub. The Clock Domain Synchronizer provides the clock domain crossing logic between the applicable PLB clocked logic and the logic synchronized to the ULPI clock (60MHz input from PHY). This synchronizing logic includes various double registered bit synchronizers and 4 asynchronous FIFOs used for the Control, Status, and In/Out Data transfers between the Link Manager and the EHCI Controller.

# **Typical System Interconnect**

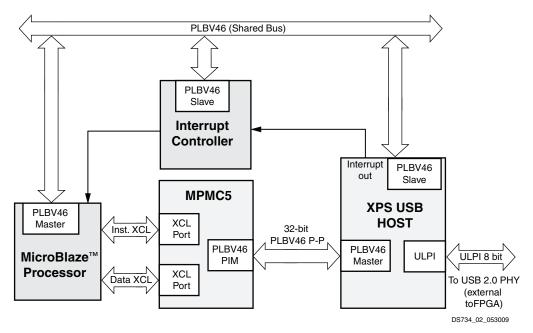

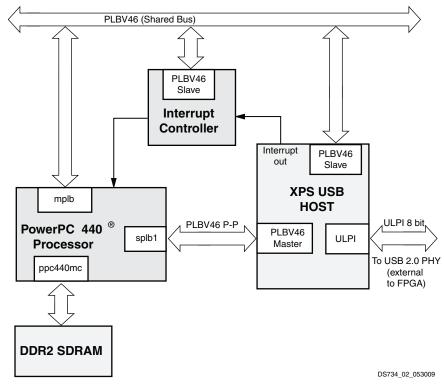

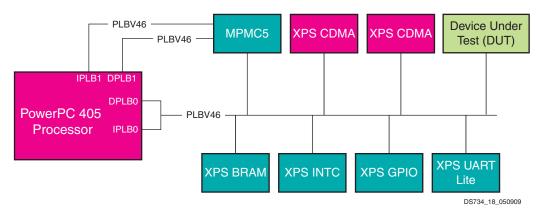

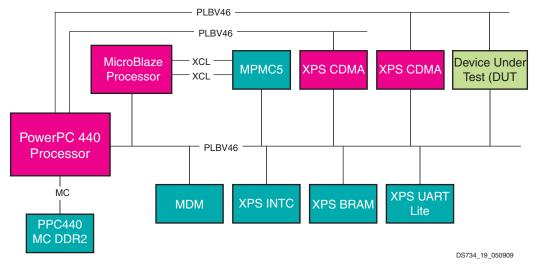

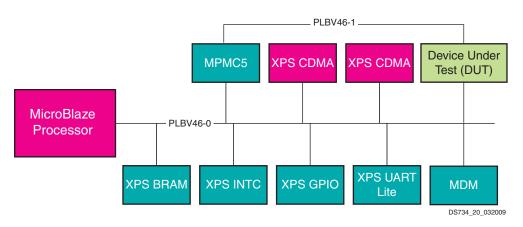

The USB Host core is designed to be connected via PLBv46 in the User's System. A typical MicroBlaze processor configuration is shown in Figure 2. A typical PPC440 system is shown in Figure 3. The System's microprocessor has access to the USB Host registers via the PLBV46 Slave Interface. An integral DMA Engine coordinates high speed data transfer between the Host Core and the System Memory via the PLBV46 Master interface. The PLBV46 Master interface may be directly connected to the multi-port memory controller (MPMC5) or PPC440 SPLB using a point to point topology or to a PLBV46 shared bus configuration (not shown). The Host Core is connected to the USB 2.0 PHY (external to the FPGA) via the 8-bit ULPI interface. The PLBV46 Master and Slave interfaces utilize the PLBV46 clock. The single interrupt output of the USB Host Core is routed to the System Interrupt Controller.

Figure 2: Typical MicroBlaze Processor System Configuration

Figure 3: Typical PPC440 Processor System Configuration

# I/O Signals

The XPS USB High Speed Host Controller signals are listed and described in Table 1.

| Signal Name         | Interface                | Signal<br>Type | Init<br>Status | Description                                                                                                                  |  |  |  |  |

|---------------------|--------------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     | System Signals           |                |                |                                                                                                                              |  |  |  |  |

| Port_Indicator(1:0) | Port<br>Indicator<br>LED | 0              | "00"           | USB Port Indicator LED control bits (per EHCI<br>Spec.)<br>"00" = off<br>"01" = Amber<br>"10" = Green"<br>"11" = Not defined |  |  |  |  |

| Host_Intr_out       | Interrupt                | 0              | 0              | Interrupt output to System Interrupt Controlle<br>or Processor                                                               |  |  |  |  |

|                     | Р                        | LB Slave Inte  | erface Inpu    | t Signals                                                                                                                    |  |  |  |  |

| SPLB_Clk            | PLB Slave                | Ι              |                | PLB System synchronization Clock                                                                                             |  |  |  |  |

| SPLB_Rst            | PLB Slave                | I              |                | PLB System PLB Reset                                                                                                         |  |  |  |  |

| PLB_ABus(0:31)      | PLB Slave                | l              |                | PLB address bus                                                                                                              |  |  |  |  |

| PLB_UABus(0:31)     | PLB Slave                | I              |                | PLB upper address bus                                                                                                        |  |  |  |  |

| PLB_PAValid         | PLB Slave                | I              |                | PLB primary address valid indicator                                                                                          |  |  |  |  |

| PLB_SAValid         | PLB Slave                | I              |                | PLB secondary address valid indicator                                                                                        |  |  |  |  |

# Table 1: XPS USB Host Controller I/O Signal Description

| Signal Name                            | Interface | Signal<br>Type | Init<br>Status | Description                                      |

|----------------------------------------|-----------|----------------|----------------|--------------------------------------------------|

| PLB_rdPrim                             | PLB Slave | I              |                | PLB secondary to primary read request promotion  |

| PLB_wrPrim                             | PLB Slave | I              |                | PLB secondary to primary write request promotion |

| PLB_masterID(0:C_SPL<br>B_MID_WIDTH-1) | PLB Slave | I              |                | PLB requesting master identification             |

| PLB_abort                              | PLB Slave | l              |                | PLB bus request abort                            |

| PLB_busLock                            | PLB Slave | I              |                | PLB bus lock                                     |

| PLB_RNW                                | PLB Slave | I              |                | PLB read not write                               |

| PLB_BE(0:(C_SPLB_<br>DWIDTH / 8) -1)   | PLB Slave | I              |                | PLB byte enables                                 |

| PLB_MSize(0:1)                         | PLB Slave | I              |                | PLB master data bus size                         |

| PLB_size(0:3)                          | PLB Slave | I              |                | PLB transfer size                                |

| PLB_type(0:2)                          | PLB Slave | I              |                | PLB transfer type                                |

| PLB_lockErr                            | PLB Slave | I              |                | PLB lock error                                   |

| PLB_wrDBus(0:C_SPLB                    |           |                |                | PLB write data bus                               |

| _<br>DWIDTH -1)                        | PLB Slave | I              |                |                                                  |

| PLB_wrBurst                            | PLB Slave | I              |                | PLB burst write transfer                         |

| PLB_rdBurst                            | PLB Slave | I              |                | PLB burst read transfer                          |

| PLB_wrPendReq                          | PLB Slave | I              |                | PLB pending write request                        |

| PLB_rdPendReq                          | PLB Slave | I              |                | PLB pending read request                         |

| PLB_wrPendPri(0:1)                     | PLB Slave | I              |                | PLB pending write request priority               |

| PLB_rdPendPri(0:1)                     | PLB Slave | l              |                | PLB pending read request priority                |

| PLB_reqPri(0:1)                        | PLB Slave | l              |                | PLB current request priority                     |

| PLB_TAttribute(0:15)                   | PLB Slave | l              |                | PLB Transfer Attribute bus                       |

|                                        | PL        | B Slave Inte   | rface Outp     | ut Signals                                       |

| SI_addrAck                             | PLB Slave | 0              | '0'            | Slave address acknowledge                        |

| SI_SSize(0:1)                          | PLB Slave | 0              | Zeros          | Slave data bus size                              |

| SI_wait                                | PLB Slave | 0              | '0'            | Slave wait indicator                             |

| SI_rearbitrate                         | PLB Slave | 0              | '0'            | Slave rearbitrate bus indicator                  |

| SI_wrDAck                              | PLB Slave | 0              | '0'            | Slave write data acknowledge                     |

| SI_wrComp                              | PLB Slave | 0              | '0'            | Slave write transfer complete indicator          |

| SI_wrBTerm                             | PLB Slave | 0              | '0'            | Slave terminate write burst transfer             |

| SI_rdDBus(0:C_SPLB_<br>DWIDTH -1)      | PLB Slave | 0              | Zeros          | Slave read bus                                   |

| SI_rdWdAddr(0:3)                       | PLB Slave | 0              | Zeros          | Slave read word address                          |

| SI_rdDAck                              | PLB Slave | 0              | '0'            | Slave read data acknowledge                      |

| SI_rdComp                              | PLB Slave | 0              | '0'            | Slave read transfer complete indicator           |

| SI_rdBTerm                             | PLB Slave | 0              | '0'            | Slave read burst terminate indicator             |

# Table 1: XPS USB Host Controller I/O Signal Description

| Signal Name                            | Interface | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                                                      |  |

|----------------------------------------|-----------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SI_MBusy(0:C_SPLB_<br>NUM_MASTERS-1)   | PLB Slave | 0              | Zeros          | Slave busy indicator (1 bit for each PLB Master)                                                                                                                                                                                                                                                                 |  |

| SI_MWrErr(0:C_SPLB_<br>NUM_MASTERS-1)  | PLB Slave | 0              | Zeros          | Slave write error indicator (1 bit for each PLB Master)                                                                                                                                                                                                                                                          |  |

| SI_MRdErr(0:C_SPLB_<br>NUM_MASTERS-1)  | PLB Slave | 0              | Zeros          | Slave read error indicator (1 bit for each PLB Master)                                                                                                                                                                                                                                                           |  |

| SI_MIRQ(0:C_SPLB_<br>NUM_MASTERS-1)    | PLB Slave | 0              | Zeros          | Slave interrupt indication (1 bit for each PLB Master)                                                                                                                                                                                                                                                           |  |

|                                        | PLB       | /46 Master Ir  | nterface Ou    | itput Signals                                                                                                                                                                                                                                                                                                    |  |

| MPLB_Clk                               | PLB Mstr  | I              |                | Master PLB System synchronization Clock<br>(not used internally, SPLB_Clk is used as PLB<br>side clocking source in the XPS USB Host)                                                                                                                                                                            |  |

| MPLB_Rst                               | PLB Mstr  | I              |                | Master PLB System PLB Reset                                                                                                                                                                                                                                                                                      |  |

| MD_Error                               | Sideband  | 0              | ,0,            | Master Detected Error output. This is an active<br>high sticky bit that is set whenever the Master<br>Module encounters an error condition during<br>operation. It can only be cleared by a reset of<br>the master Module either via the PLB reset<br>input or the EHCI Controller requesting a<br>Master reset. |  |

| M_request                              | PLB Mstr  | Output         | '0'            | Master access request                                                                                                                                                                                                                                                                                            |  |

| M_priority (0:1)                       | PLB Mstr  | Output         | Zeros          | Master Request Priority qualifier                                                                                                                                                                                                                                                                                |  |

| M_buslock                              | PLB Mstr  | Output         | '0'            | Master Bus Lock Request qualifier                                                                                                                                                                                                                                                                                |  |

| M_RNW                                  | PLB Mstr  | Output         | '0'            | Master Read not Write qualifier                                                                                                                                                                                                                                                                                  |  |

| M_BE(0 :<br><b>C_MPLB_DWIDTH</b> /8-1) | PLB Mstr  | Output         | Zeros          | Master BE qualifier                                                                                                                                                                                                                                                                                              |  |

| M_MSize(0:1)                           | PLB Mstr  | Output         | Zeros          | Master Size qualifier (Native Data Width)                                                                                                                                                                                                                                                                        |  |

| M_size(0:3)                            | PLB Mstr  | Output         | Zeros          | Master Transfer Size qualifier                                                                                                                                                                                                                                                                                   |  |

| M_type(0:2)                            | PLB Mstr  | Output         | Zeros          | Master Transfer Type qualifier                                                                                                                                                                                                                                                                                   |  |

| M_TAttribute(0:15)                     | PLB Mstr  | Output         | Zeros          | Master Transfer Attributes qualifier                                                                                                                                                                                                                                                                             |  |

| M_lockErr                              | PLB Mstr  | Output         | '0'            | Master Lock Error qualifier                                                                                                                                                                                                                                                                                      |  |

| M_abort                                | PLB Mstr  | Output         | '0'            | Master request abort qualifier<br>Never asserted, Always logic '0'                                                                                                                                                                                                                                               |  |

| M_UABus(0 : 31)                        | PLB Mstr  | Output         | Zeros          | Master Upper Address qualifier<br>Always driven to zeros                                                                                                                                                                                                                                                         |  |

| M_ABus(0:31)                           | PLB Mstr  | Output         | Zeros          | Master Request Lower Address qualifier                                                                                                                                                                                                                                                                           |  |

| M_wrDBus(0 :<br>C_MPLB_DWIDTH-1)       | PLB Mstr  | Output         | Zeros          | Master Write Data Bus                                                                                                                                                                                                                                                                                            |  |

| M_wrBurst                              | PLB Mstr  | Output         | '0'            | Master Write Burst qualifier                                                                                                                                                                                                                                                                                     |  |

| M_rdBurst                              | PLB Mstr  | Output         | '0'            | Master Read Burst qualifier                                                                                                                                                                                                                                                                                      |  |

|                                        | PLB       | V46 Master     | Interface In   | put Signals                                                                                                                                                                                                                                                                                                      |  |

| PLB_MAddrAck                           | PLB Mstr  | Input          |                | PLB Address Acknowledge                                                                                                                                                                                                                                                                                          |  |

| PLB_MSSize(0:1)                        | PLB Mstr  | Input          |                | PLB Slave Size indication                                                                                                                                                                                                                                                                                        |  |

| Signal Name                         | Interface                                       | Signal<br>Type | Init<br>Status | Description                                                                                                                                                                                                                                                                      |

|-------------------------------------|-------------------------------------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLB_MRearbitrate                    | PLB Mstr                                        | Input          |                | PLB Slave Rearbitrate indication                                                                                                                                                                                                                                                 |

| PLB_MTimeout                        | PLB Mstr                                        | Input          |                | PLB Bus Timeout indication                                                                                                                                                                                                                                                       |

| PLB_MBusy                           | PLB Mstr                                        | Input          |                | PLB Slave Busy indication                                                                                                                                                                                                                                                        |

| PLB_MRdErr                          | PLB Mstr                                        | Input          |                | PLB Slave Read Error indication                                                                                                                                                                                                                                                  |

| PLB_MWrErr                          | PLB Mstr                                        | Input          |                | PLB Slave Write Error indication                                                                                                                                                                                                                                                 |

| PLB_MIRQ                            | PLB Mstr                                        | Input          |                | PLB Slave Interrupt request<br>Not used by the Master Interface                                                                                                                                                                                                                  |

| PLB_MRdDBus(0 :<br>C_MPLB_DWIDTH-1) | PLB Mstr                                        | Input          |                | PLB Read Data Bus                                                                                                                                                                                                                                                                |

| PLB_MRdWdAddr(0:3)                  | PLB Mstr                                        | Input          |                | PLB Read Word Address<br>Not used by the Master                                                                                                                                                                                                                                  |

| PLB_MRdDAck                         | PLB Mstr                                        | Input          |                | PLB Read Data Acknowledge                                                                                                                                                                                                                                                        |

| PLB_MRdBTerm                        | PLB Mstr                                        | Input          |                | PLB read Burst Terminate                                                                                                                                                                                                                                                         |

| PLB_MWrDAck                         | PLB Mstr                                        | Input          |                | PLB Write Data Acknowledge                                                                                                                                                                                                                                                       |

|                                     |                                                 | USB            | PHY Reset      |                                                                                                                                                                                                                                                                                  |

| USB_PHY_Reset                       | USB PHY<br>(Not a<br>ULPI<br>defined<br>signal) | 0              | 0              | Active high auxiliary reset for external USB<br>PHY connection. It echoes the internal<br>hardware reset used by the XPS USB Host<br>design.<br>Note that is this signal may or may not be used.<br>This is dependent on the User's USB PHY<br>circuit design and PHY selection. |

|                                     | ULPI Interface Signals                          |                |                |                                                                                                                                                                                                                                                                                  |

| ULPI_Clock                          | ULPI                                            | 1              | N/A            | 60MHz input clock from the ULPI PHY used for<br>synchronization within the XPS USB Host<br>(Link Manager is synchronized with this clock)                                                                                                                                        |

| ULPI_Dir                            | ULPI                                            | I              | N/A            | <b>Direction:</b> Direction of data flow between Host and ULPI PHY (See ULPI V1.1 Spec)                                                                                                                                                                                          |

| ULPI_Stp                            | ULPI                                            | 0              | 0              | <b>Stop:</b> Indicator that transmission of last byte is complete (See ULPI V1.1 Spec)                                                                                                                                                                                           |

| ULPI_Nxt                            | ULPI                                            | I              | N/A            | <b>Next:</b> Indicator of when the PHY is ready for the next byte (See ULPI V1.1 Spec)                                                                                                                                                                                           |

| ULPI_Data_I(7:0) (1)                | ULPI                                            | I              | N/A            | Input Data: Input data to the core from the ULPI PHY (See ULPI V1.1 Spec)                                                                                                                                                                                                        |

| ULPI_Data_O(7:0)                    | ULPI                                            | 0              | Zeros          | Output Data: Output data from the Host to the ULPI PHY (See ULPI V1.1 Spec)                                                                                                                                                                                                      |

| ULPI_Data_T(7:0)                    | ULPI                                            | 0              | 0              | <b>Tri-state:</b> ULPI_Data is a 3-state port, with ULPI_Data_I as the IN port, ULPI_Data_O as the OUT port and ULPI_Data_T as the tristate output. One for one bit match to data bits.                                                                                          |

#### Table 1: XPS USB Host Controller I/O Signal Description

1. The ULPI Data bus is defined in the ULPI specification as a bi-directional bus. Bi-directional buses are not supported within the targeted FPGA families for this core. Therefore bi-dir buses are split into an input bus, an output bus, and a direction control. Using standardize Xilinx notation, these are converted to a true bi-directional bus at the FPGA I/O pin boundary (external to this core design)

# **XPS USB Host Controller Parameters**

To allow the user to obtain an XPS USB HS Host Controller that is uniquely tailored for their system, certain features can be parameterized in the XPS USB HS Host Controller design. This allows the configuration of a design that utilizes only the resources required by the system and that operates with the best possible performance. The features that can be parameterized in Xilinx XPS USB HS Host Controller design are shown in Table 2.

| Feature/Description                                                                                                                                          | Parameter<br>Name                  | Allowable Values                                                                                                   | Default<br>Values | VHDL<br>Type         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|--|

|                                                                                                                                                              | General Host I                     | Parameters                                                                                                         |                   |                      |  |

| Enable Host Support of USB Full<br>Speed devices                                                                                                             | C_SUPPORT_<br>USB_FS               | 0, 1<br>0 = High Speed device<br>support only<br>1= High Speed device<br>support plus Full Speed<br>device Support | 1                 | integer              |  |

| Indication that Host can control the<br>USB power via User's external PHY<br>circuit                                                                         | C_HAS_PWR_<br>CNTL                 | 0,1<br>0 = Host Power Control is<br>not available<br>1 = Host Power control is<br>available                        | 1                 | integer              |  |

| Indicates if the User's external circuit<br>design requires the PHY to provide<br>VBus power from it's internal charge<br>pump                               | C_USE_PHY_<br>BUS_PWR              | 0 = External PHY not<br>sourcing VBus power<br>1 = PHY is sourcing VBus<br>Power                                   | 0                 | Integer              |  |

| Indicates if the User's external PHY<br>circuit needs to provide the VBus<br>valid indicator to the PHY from a<br>source outside of the PHY                  | C_EXT_VBUS_<br>VALID               | 0 = Use internal PHY<br>VBus valid comparator<br>1 - Use External VBus<br>valid indicator                          | 1                 | integer              |  |

| Indicates if the User's external VBus<br>valid indicator to the PHY (if used)<br>needs to be inverted by the PHY for<br>proper interpretation                | C_EXT_VBUS_<br>VALID_INVERT        | 0 = Don't Invert external<br>Vbus valid input<br>1 = Invert external Vbus<br>valid input                           | 0                 | integer              |  |

| PI                                                                                                                                                           | BV46 Master Inter                  | rface Parameters                                                                                                   | L                 |                      |  |

| Width of the PLB Address Bus to which the Master is attached                                                                                                 | C_MPLB_<br>AWIDTH                  | 32 (1)                                                                                                             | 32 (2)            | integer              |  |

| Width of the PLB Data Bus to which the Master is attached                                                                                                    | C_MPLB_<br>DWIDTH                  | 32, 64, 128                                                                                                        | 32                | integer              |  |

| Specifies the connection topology of<br>the PLBV46 attachment to the<br>PLBV46 Master port. This is currently<br>not used in the PLBV46 Master<br>interface. | C_MPLB_P2P                         | 0, 1<br>0 = Shared Bus PLBV46<br>(Normal)                                                                          | 0                 | integer              |  |

| PLBV46 Slave Interface Parameters                                                                                                                            |                                    |                                                                                                                    |                   |                      |  |

| PLB Slave Register Base Address assignment                                                                                                                   | C_SPLB_<br>BASEADDR <sup>(3)</sup> | System Address value of C_SPLB_AWIDTH bits wide                                                                    | FFFF_FFFF         | std_logi<br>c_vector |  |

| Table 2: XPS USB Host Controller Design F | Parameters |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| Feature/Description                                                           | Parameter<br>Name                | Allowable Values                                                      | Default<br>Values  | VHDL<br>Type         |  |

|-------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|--------------------|----------------------|--|

| PLB Slave Register HIGH Address assignment                                    | C_SPLB_<br>HIGHADDR              | System Address value of<br>C_SPLB_AWIDTH bits<br>wide                 | 0000_0000          | std_logi<br>c_vector |  |

| Width of the PLB Address Bus Width to which the Slave is attached             | C_SPLB_<br>AWIDTH <sup>(4)</sup> | 32                                                                    | 32                 | integer              |  |

| Width of the PLB Data bus to which the Slave is attached                      | C_SPLB_<br>DWIDTH                | 32, 64, or 128                                                        | 32                 | integer              |  |

| Number of PLB Masters present on<br>the PLB to which the Slave is<br>attached | C_SPLB_NUM_<br>MASTERS           | 1 - 16                                                                | 1                  | integer              |  |

| PLB Width of Master ID Bus of the PLB to which the Slave is attached          | C_SPLB_MID_<br>WIDTH             | roundup(log <sub>2</sub> (C_SPLB_N<br>UM_MASTERS))                    | 1                  | integer              |  |

| Configures the Slave for Point to Point<br>PLB Optimizations                  | C_SPLB_P2P <sup>(5)</sup>        | 0,1<br>0 = Shared Bus PLBV46<br>(Normal)<br>1 = Point to Point PLBV46 | 0                  | Integer              |  |

| Period of the SPLB_Clk in pico-<br>seconds                                    | C_SPLB_CLK_<br>PERIOD_PS         | 5000 to 16666<br>(200MHz to 60MHZ) <sup>(6)</sup>                     | 10,000<br>(100MHz) | integer              |  |

| Target FPGA Family Parameter                                                  |                                  |                                                                       |                    |                      |  |

| Target FPGA device family                                                     | C_FAMILY                         | "spartan3a", "spartan6,<br>"virtex4", "virtex5",<br>"virtex6"         | "virtex5"          | String               |  |

#### Table 2: XPS USB Host Controller Design Parameters

Xilinx EDK limits addressing to 32 bits.

Default values are specified for C\_BASEADDR and C\_HIGHADDR to ensure that they are set by the user. If the value is not set, an implementation error will be generated.

C\_BASEADDR value must be a power of 2 and a multiple of 512 bytes.

C\_BASEADDR value must be a power of 2 and a multiple of 512 bytes.

These parameters are calculated and automatically assigned by the EDK XPS tools during the system creation process.

Point to point optimizations include removal of address decoding. This mode is not usable in a shared bus interconnect environment.

The parameter allows for specification of up to 200 MHz, but the core is rated only for those frequencies specified in Table 24, "USB Host Controller System Performance," on page 45.

# **Allowable Parameter Combinations**

| Table | 3: | Allowable | Parameter | Combinations |

|-------|----|-----------|-----------|--------------|

|-------|----|-----------|-----------|--------------|

| Parameter Name         | Affects Parameter                   | Relationship Description                                    |

|------------------------|-------------------------------------|-------------------------------------------------------------|

| C_HAS_PWR_CNTL         | C_USE_PHY_BUS_PWR                   | Affected Parameter is ignored when<br>C_HAS_PWR_CNTL = 0    |

| C_HAS_PWR_CNTL         | C_EXT_VBUS_VALID                    | Affected Parameter is ignored when<br>C_HAS_PWR_CNTL = 0    |

| C_HAS_PWR_CNTL         | C_EXT_VBUS_VALID_INVER<br>T         | Affected Parameter is ignored when<br>C_HAS_PWR_CNTL = 0    |

| C_EXT_VBUS_VALID       | C_EXT_VBUS_VALID_INVER<br>T         | Affected Parameter is ignored when<br>C_EXT_VBUS_VALID = 0  |

| C_SPLB_NUM_MASTER<br>S | C_SPLB_MID_WIDTH                    | C_SPLB_MID_WIDTH must equal log2(C_SPLB_NUM_MASTERS)        |

| C_SPLB_AWIDTH          |                                     | Always set to 32                                            |

| C_MPLB_AWIDTH          |                                     | Always set to 32                                            |

| C_SPLB_P2P             | C_SPLB_BASEADDR,<br>C_SPLB_HIGHADDR | Affected parameters are ignored when<br>C_SPLB_P2P = 1      |

| C_USE_PHY_BUS_PWR      | C_EXT_VBUS_VALID                    | Affected parameter is ignored when<br>C_USE_PHY_BUS_PWR = 1 |

| C_USE_PHY_BUS_PWR      | C_EXT_VBUS_VALID_INVER<br>T         | Affected parameter is ignored when C_USE_PHY_BUS_PWR = 1    |

# **Parameter - Port Dependencies**

## Table 4: XPS USB Host Controller Parameter-Port Dependencies

| Generic<br>ID | Generic Name           | Affects Port                                     | Depends<br>on<br>Parameter | Relationship Description                                         |

|---------------|------------------------|--------------------------------------------------|----------------------------|------------------------------------------------------------------|

|               |                        | Desig                                            | n Parameters               |                                                                  |

| G1            | C_SPLB_NUM_<br>MASTERS | SI_MBusy,<br>SI_MWrErr,<br>SI_MRdErr,<br>SI_MIRQ |                            | Port widths are set directly from the parameter value            |

| G2            | C_SPLB_MID_<br>WIDTH   | PLB_masterID                                     |                            | Port widths are set directly from the parameter value            |

| G3            | C_SPLB_DWIDTH          | PLB_BE,<br>PLB_wrDBus,<br>SI_rdDBus              |                            | Port widths are set directly or derived from the parameter value |

| G3            | C_MPLB_DWIDTH          | M_BE,<br>M_wrDBus,<br>PLB_MrdDBus                |                            | Port widths are set directly or derived from the parameter value |

# **Parameter Descriptions**

# C\_SUPPORT\_USB\_FS

Type: Integer

**Allowed Values:** 0,1 (default = 1)

**Definition:** 0 = HS only devices, 1 = Support HS and FS devices.

**Description:** This integer parameter is used to control inclusion or omission of Full Speed (FS) device support in the Host. When this parameter is assigned a value of 1, the Transaction Translator is included in the Link Manager and EHCI Split Transfer Support is added to the EHCI Controller. This increases the resource utilization of the core significantly.

# C\_HAS\_PWR\_CNTL

Type: Integer

Allowed Values: 0,1 (default = 1)

Definition: 0 = User has not provided for Vbus power control, 1 = Power Control is provided

**Description:** This integer parameter indicates to the Host that the User has provided the capability for the Host to control the USB Power Bus via a discrete switch or the PHY. The state of this parameter is echoed in the PPC bit of the **HCSPARAMS** register. 0 = Port Power Control not available, 1 = Port Power Control is provided. The parameter is defaulted to 1, which indicates the Host has the ability to control Vbus power.

# C\_USE\_PHY\_BUS\_PWR

Type: Integer

Allowed Values: 0,1 (default = 0)

**Definition:** 0 = PHY is not providing Vbus power, 1 = PHY is providing Vbus power

**Description:** This integer parameter indicates to the Host that the User circuit design is providing USB power on Vbus from the charge pump of the PHY (not an external switch). The parameter is defaulted to 1, indicating that the USB Vbus power will be provided by the PHY device. An assigned value of 0 indicates the User's design is supplying Vbus power from a source other than the PHY.

# C\_EXT\_VBUS\_VALID

Type: Integer

Allowed Values: 0,1 (default = 1)

**Definition:** 0 = Use PHY internal Vbus valid monitor, 1 = Use PHY external input for Vbus Valid indication

**Description:** This integer parameter indicates to the Host if the User PHY will be using a Vbus Valid input from a monitoring source external of the PHY or if the PHY will be providing the monitoring function. The parameter is defaulted to 1, indicating an external monitoring source is being used (the PHY is using an external Vbus Valid indication).

# C\_EXT\_VBUS\_VALID\_INVERT

Type: Integer

Allowed Values: 0,1 (default = 0)

Definition: 0 = Use Vbus Valid input non-inverted, 1 = Invert the Vbus Valid input to the PHY

**Description:** If the PHY is using an external Vbus monitor ( $C\_EXT\_VBUS\_VALID = 1$ ), then this parameter indicates to the Host that the PHY should be programmed to invert the sense of the external power valid input signal. The parameter is defaulted to 0, indicating no inversion. Note that this parameter only has meaning if the  $C\_EXT\_VBUS\_VALID$  parameter is set to 1.

## C\_MPLB\_AWIDTH

Type: Integer

Allowed Values: 32

Definition: Address bus width of attached PLB on the Master interface

**Description:** This integer parameter is used by the PLB Master to size the PLB address related components within the Master. The EDK tool suite will assign this parameter a fixed value of 32.

#### C\_MPLB\_DWIDTH

Type: Integer

Allowed Values: 32, 64, 128

Definition: Data bus width of attached PLB on the Master interface

**Description:** This integer parameter is used by the PLB Master to configure PLB data bus attachment logic within the Master. The parameter can be assigned a value of 32, 64 or 128-Bits. The EDK tools will ensure that the attached PLB data width is equal to or greater than the Native data with of any Master or Slave attached to the PLB.

## C\_MPLB\_P2P

Type: Integer

Allowed Values: 0,1 (default = 0)

Definition: 0 = Shared Bus PLBV46 topology, 1 = Point to Point PLBV46 topology

Description: This integer parameter indicates the type of connection topology for the PLBV46 attached to the Master port.

#### C\_SPLB\_BASEADDR

**Type:** std\_logic\_vector(0 to 31)

Allowed Values: 0000\_0000 to FFFF\_FE00 (default = FFFF\_FFF)

Definition: 32-bit system address

**Description:** This 32-bit parameter is a std\_logic\_vector and is used to assign the start of the system memory mapped address range assigned for the EHCI register set within the USB Host. The address value assigned must start on an even multiple of the address space that the User wishes to assign to the Host's Slave PLB port. Minimum system address space required for the USB Host is 200<sub>hex</sub> bytes.

## C\_SPLB\_HIGHADDR

**Type:** std\_logic\_vector(0 to 31)

Allowed Values: 0000\_01FF to FFFF\_FFFF (default = 0000\_0000)

Definition: 32-bit system address

**Description:** This 32-bit parameter is a std\_logic\_vector and is used to assign the end of the assigned system memory mapped address range for the EHCI register set within the USB Host. This parameter must be assigned an address value that reflects the assigned address space to the Registers. If the recommended  $200_{hex}$  byte address space allocation is utilized, then the assigned value for this parameter should be C\_SPLB\_BASEADDR + 1FF<sub>hex</sub>.

### C\_SPLB\_MID\_WIDTH

Type: Integer

Allowed Values: 1 to 4

Definition: Sets the width of the PLB\_masterID input port

**Description:** This parameter is set to indicate the bit width of the PLB\_masterID input port. The assigned value must be equal to log2(C\_SPLB\_NUM\_MASTERS);

### C\_SPLB\_NUM\_MASTERS

Type: Integer

Allowed Values: 1 to 16

**Definition:** 1 = 1 PLB Master, 2 = 2 PLB Masters, etc.

**Description:** This parameter is set to indicate the number of Masters connected to the Slave PLB bus. This parameter is used to size the Sl\_MBusy and Sl\_MErr slave reply buses to the PLB. For example, if eight PLB Masters are connected to the PLB Bus, then this parameter must be set to 8. The Sl\_MBusy bus and Sl\_MErr bus will be sized to 8 bits wide each.

#### C\_SPLB\_AWIDTH

Type: Integer

Allowed Values: 32

Definition: Address bus width of attached PLB on the Slave interface

**Description:** This integer parameter is used by the PLB Slave to size the PLB address related components within the Slave Attachment. The EDK tool suite will assign this parameter a fixed value of 32.

#### C\_SPLB\_DWIDTH

Type: Integer

Allowed Values: 32, 64, 128

Definition: Data bus width of attached PLB on the Slave interface

**Description:** This integer parameter is used by the PLB Slave to size PLB data bus related components within the Slave Attachment. This value should be set to match the actual width of the PLB bus, 32, 64 or 128-Bits.

# C\_SPLB\_P2P

Type: Integer

Allowed Values: 0,1 (default = 0)

**Definition:** 0 = Shared Bus PLBV46 topology, 1 = Point to Point PLBV46 topology

**Description:** This integer parameter indicates the type of connection topology for the PLBV46 attached to the Slave port.

# C\_SPLB\_CLK\_PERIOD\_PS

Type: Integer

Allowed Values: 16,666 (60MHz) to 5000 (200MHz) (default = 10,000 (100MHz))

Definition: Clock period in picoseconds of the input clock on the PLBV46 Slave interface

**Description:** This integer parameter specifies the period of the input SPLB\_Clk. It is used by internal logic to set timer count values that are clocked off of the SPLB\_Clk clock signal. The actual  $F_{MAX}$  frequencies obtainable are system dependent and indicated in Table 24.

## C\_FAMILY

Type: String

Allowed Values: "spartan3", "virtex4", "virtex5"

Definition: Family of target FPGA device

**Description:** This parameter is defined as a string. It specifies the target FPGA technology for implementation of the PLB Slave. This parameter is required for proper selection of FPGA primitives. The configuration of these primitives can vary from one FPGA technology family to another. FPGA families supported are Spartan-3, Virtex-4, Virtex-5 FPGAs.

# **XPS USB Host Registers**

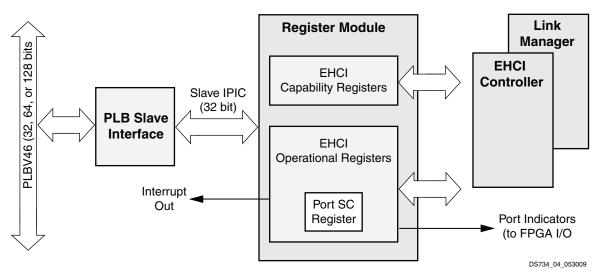

All User accessible register functions (via the PLBV46 Slave interface) for the USB Host are encapsulated in the Register Module. The module is partitioned into 2 sub-blocks, the EHCI Capability Register, and the EHCI Operational registers. The Register Module Block Diagram is shown in Figure 4.

The Register Module interfaces to the PLBV46 Slave Single module on the System Interface and with the internal USB Host logic. The internal logic side of the Register Module has varying set/reset/access requirements based on the individual register and the bit/field within each register. The XPS USB Host Controller complies with the Intel Enhanced Host Controller Interface (EHCI) version 1.0 with those exceptions listed in section "Specification Exceptions". EHCI calls out two major sets of software accessible hardware registers. Memory mapped Host Controller Registers and optional PCI configuration registers. The USB Host soft core does not have a PCI interface so the PCI configuration registers are omitted from the design.

Figure 4: Register Module Block Diagram

# **Register Space Partitioning**

The general USB Host soft core register space partitioning is shown in Table 5. The USB Host Controller Registers are memory-mapped into non-cacheable memory space. This memory space must be aligned on a PLB word (32-bit) address boundary.

| Address Space<br>Offset <sup>(1)</sup> | Register Group                | Description                                                                                                                                                                                                             |

|----------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000 <sub>H</sub> - 0FC <sub>H</sub>    | Xilinx Reserved (2)           | Xilinx Reserved                                                                                                                                                                                                         |

| 000 <sub>H</sub> - 0FC <sub>H</sub>    | Xilinx Reserved               | Xilinx Reserved                                                                                                                                                                                                         |

| 100 <sub>H</sub> - 124 <sub>H</sub>    | EHCI Capability<br>Registers  | EHCI Capability Registers. The Capability registers specify<br>the limits, restrictions, and capabilities of a host controller<br>implementation. These values are used as parameters to the<br>host controller driver. |

| 140 <sub>H</sub> - 1FC <sub>H</sub>    | EHCI Operational<br>Registers | EHCI Operational Registers. The operational registers are<br>used by system software to control and monitor the<br>operational state of the host controller.                                                            |

Table 5: General XPS USB Host Register Partition Address Mapping

1. Address Space Offset is relative to C\_SPLB\_BASEADDR assignment.

2. Reserved memory space partition for Xilinx internal testing use only.

# **EHCI Register Definitions**

The reserved bits defined in EHCI version 1.0 of the specification may be allocated in later revisions. Software should not assume reserved bits are always zero and should preserve these bits when writing to modifiable registers. Per the EHCI specification, the following notation is used to describe register access attributes:

- **RO (Read Only)**. If a register is read only, writes have no effect.

- WO (Write Only). If a register is write only, reads return a zero for all bit positions.

- **R/W (Read/Write)**. A register with this attribute can be read and written. Note that individual bits in some read/write registers may be read only.

• **R/WC (Read/Write Clear)**. A register bit with this attribute can be read and written. However, a write of a 1 clears (sets to 0) the corresponding bit and a write of a 0 has no effect.

All Registers in the XPS USB Host are powered by the FPGA power which is considered the core power well from the EHCI perspective. There are no auxiliary or PCI power considerations for this core.

# **EHCI Register Endianess Considerations**

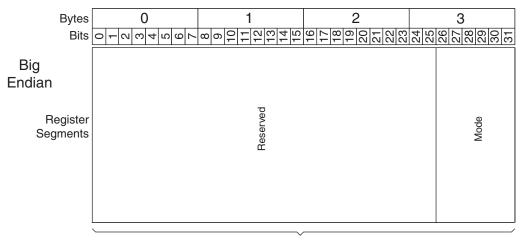

The EHCI specification is targeted for a little endian processor environment. However the Xilinx Micro-Blaze and PowerPC processor embedded systems are natively big endian due to their basis in the IBM CoreConnect Architecture. The EHCI register interfaces for the Xilinx USB Host are presented in this document in the big endian format. The relative bit significance of the registers are the same as EHCI, Most significant is left-most, Least Significant is right-most. If the registers are accessed as 32-bit values by the system software, then the endiness is transparent. The only exception to this is the CAPLENGTH\_HCIVERSION register which is required by the LINUX programming model to allow access to the CAPLENGTH and HCI Version fields as separate entities. This register has been formatted to support that requirement. The XPS USB Host Controller does not provide any endianess conversion features.

## Host Controller Capability Registers

These registers specify the limits, restrictions and capabilities of the Xilinx USB Host Controller implementation. Table 6 provides address offset and name information.

| Address Offset (From<br>Capabilities Base<br>Address) | Size<br>(bytes) | Mnemonic       | Register Name                                   |

|-------------------------------------------------------|-----------------|----------------|-------------------------------------------------|

| 00h                                                   | 1               | CAPLENGTH      | Capability Register Length                      |

| 01h                                                   | 1               | Reserved       | N/A                                             |

| 02h                                                   | 2               | HCIVERSION     | Interface Version Number                        |

| 04h                                                   | 4               | HCSPARAMS      | Structural Parameters                           |

| 08h                                                   | 4               | HCCPARAMS      | Capability Parameters                           |

| 0Ch                                                   | 8               | HCSP-PORTROUTE | Companion Port Route Description <sup>(1)</sup> |

Table 6: Enhanced Host Controller Capability Registers Summary

1. This register is required only if companion host controllers are implemented. This host controller does not have companion controllers, therefore this register is not provided as part of this design.

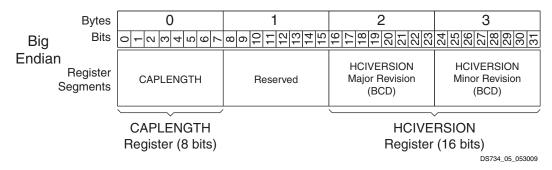

## CAPLENGTH\_HCIVERSION (Capability Registers Length/Host Controller Version)

This register has two fields as shown in Figure 5. The first field (CAPLENGTH) is a 1 byte value that is used as an offset to add to the register address base to find the beginning of the Operational Register Space. The second field (HCIVERSION) is a two-byte register containing a BCD encoding of the EHCI revision number supported by this host controller. The most significant byte of this field represents a major revision and the least significant byte is the minor revision. Table 7 provides information about this register.

#### **Big-endian/little-endian compatibility note:**

The CAPLENGTH value must be accessed by software as a 1-byte entity and the HCIVERSION must be accessed as a 2-byte (PLB Half-word) entity. The byte offset into the register for these values has been adjusted for this type of access.

#### Figure 5: CAPLENGTH\_HCIVERSION Register Layout

| Table 7: CAPLENGTH_HCIVERSION Details | s |

|---------------------------------------|---|

|---------------------------------------|---|

| Bits  | Field Name            | Default<br>Value  | Access<br>Type | Description                                                                                                                                                                                                      |

|-------|-----------------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7   | CAPLENGTH             | 40 <sub>hex</sub> | RO             | The length (in bytes) of the capability register space.<br>This value is added (as an address offset to the<br>Capabilities register base address) to get to the<br>address space for the Operational Registers. |

| 8-15  | Reserved              | Zeros             | RO             | These bits are reserved and set to zero.                                                                                                                                                                         |

| 16-23 | HCIVERSION<br>(major) | 01 <sub>hex</sub> | RO             | This field is a BCD encoding of the major version number of the supported EHCI specification revision.                                                                                                           |

| 24-31 | HCIVERSION<br>(minor) | 00 <sub>hex</sub> | RO             | This field is a BCD encoding of the minor version number of the supported EHCI specification revision.                                                                                                           |

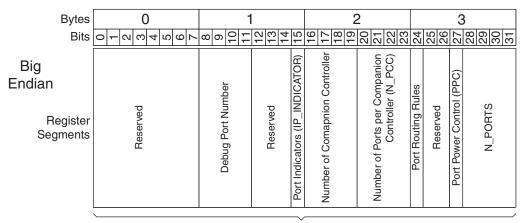

#### HCSPARAMS (Host Controller Structural Parameters)

This register contains the parameters that provide structural composition of the host controller to the user application or RTOS. The register format is shown in Figure 6 and described in Table 8.

#### **Big-endian/little-endian compatibility note:**

The HCSPARAMS value must be accessed as a 4-byte (PLB word) entity.

HCSPARAMS Register (32 bits)

DS734\_06\_053009

#### Figure 6: HCSPARAMS Register Layout

| Bits  | Field Name                                     | Default<br>Value | Access<br>Type | Description                                                                                                               |

|-------|------------------------------------------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| 0-7   | Reserved                                       | Zeros            | RO             | These bits are reserved and set to zero.                                                                                  |

| 8-11  | Debug Port<br>Number                           | Zeros            | RO             | Debug port is not supported so this field is set to a constant zero.                                                      |

| 12-14 | Reserved                                       | Zeros            | RO             | These bits are reserved and set to zero.                                                                                  |

| 15    | Port Indicators                                | 1                | RO             | Port Indicator support is parameterizable so this field reflects the value of the <b>C_HAS_PORT_INDICATORS</b> parameter. |

| 16-19 | Number of<br>Companion<br>Controllers          | Zeros            | RO             | There are no companion controllers, so this field is set to constant 0.                                                   |

| 20-23 | Number of Ports<br>per Companion<br>Controller | Zeros            | RO             | There are no companion controllers, so this field is set to constant 0.                                                   |

| 24    | Port Routing Rules                             | 0                | RO             | Because no companion controllers are used, this value is set to a constant 0.                                             |

| 25-26 | Reserved                                       | Zeros            | RO             | These bits are reserved and set to zero.                                                                                  |

| 27    | Port Power Control                             | 1                | RO             | Port Power Control is parameterizable so this field reflects the value of the <b>C_HAS_PWR_CNTL</b> parameter.            |

| 28-31 | Number of Ports                                | 1                | RO             | This bit set to a constant 1. This Host Controller implements only 1 port.                                                |

#### Table 8: HCSPARAMS Details

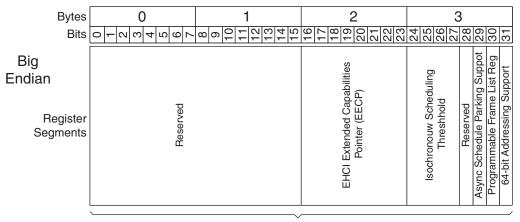

#### HCCPARAMS (Capability Parameters)

This register provides the Host Controller capabilities parameters. The register layout is shown in Figure 7 and the register fields are described in Table 9.

#### **Big-endian/little-endian compatibility note:**

The HCSPARAMS value must be accessed by software as a 4-byte (PLB word) entity.

HCSPARAMS Register (32 bits)

DS734\_07\_050109

Figure 7: HCCPARAMS Register

| Bits  | Field Name                               | Default<br>Value | Access<br>Type | Description                                                                                                      |

|-------|------------------------------------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------|

| 0-15  | Reserved                                 | Zeros            | RO             | These bits are reserved and set to zero.                                                                         |

| 16-23 | EHCI Extended<br>Capabilities<br>Pointer | Zeros            | RO             | This Host does not have Extended Capabilities so this field is set to constant zeros.                            |

| 24-27 | Isochronous<br>Scheduling<br>Threshold   | "1000"           | RO             | Set to constant "1000". The EHCI Controller will cache<br>a full isochronous data structure for an entire Frame. |

| 28    | Reserved                                 | 0                | RO             | This bit is reserved and set to 0.                                                                               |

| 29    | Asynchronous<br>Parking Support          | 1                | RO             | Set to constant 1. This Host supports Asynchronous Schedule Parking.                                             |

| 30    | Programmable<br>Frame List Support       | 1                | RO             | This Host Controller supports programmable frame list length.                                                    |

| 31    | 64-bit Addressing<br>Support             | 0                | RO             | This Host does not support 64-bit addressing.                                                                    |

Table 9: HCCPARAMS Details

#### HCSP-PORTROUTE (Companion Port Route)

This is an optional EHCI register set. It is not provided by this Host Controller because companion host controllers are not implemented in the design.

# **Host Controller Operational Registers**

This section defines the enhanced host controller operational registers. These registers are located after the capabilities registers. The operational register base are PLB Word (32-bit) aligned and is calculated by adding the value in the first capabilities register (CAPLENGTH) to the base address of the enhanced host controller register address space. All registers are 32 bits in length. Software must read and write these registers using only PLB Word (32-bit) accesses to maintain the proper big-endian to little-endian overlay.

| Operational<br>Register<br>Space Offset | Size<br>(bytes) | Mnemonic         | Register Name                  |

|-----------------------------------------|-----------------|------------------|--------------------------------|

| 00h                                     | 4               | USBCMD           | USB Command                    |

| 04h                                     | 4               | USBSTS           | USB Status                     |

| 08h                                     | 4               | USBINTR          | USB Interrupt Enable           |

| 0Ch                                     | 4               | FRINDEX          | USB Frame Index                |

| 10h                                     | 4               | CTRLDSSEGMENT    | 4G Segment Selector            |

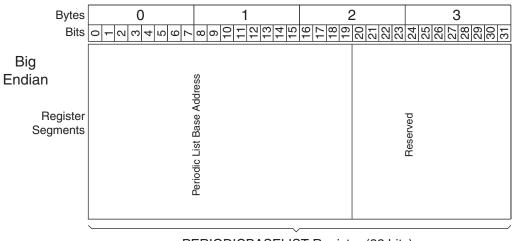

| 14h                                     | 4               | PERIODICLISTBASE | Frame List Base Address        |

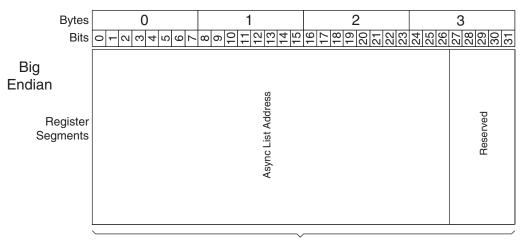

| 18h                                     | 4               | ASYNCLISTADDR    | Next Asynchronous List Address |

| 1Ch-3Fh                                 | 36              | Reserved         |                                |

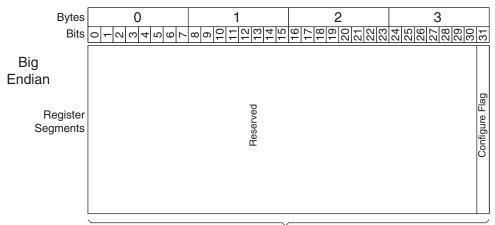

| 40h                                     | 4               | CONFIGFLAG       | Configured Flag Register       |

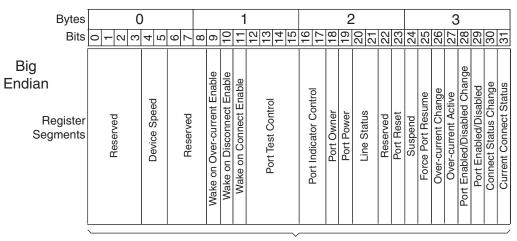

| 44h                                     | 4               | PORTSC           | Port Status/Control Register   |

| 48h-A4h                                 |                 | Reserved         |                                |

Table 10: Host Controller Operational Registers

| Table | 10: | Host | Controller | Operational | Registers |

|-------|-----|------|------------|-------------|-----------|

|-------|-----|------|------------|-------------|-----------|

| Operational<br>Register<br>Space Offset | Size<br>(bytes) | Mnemonic | Register Name                |

|-----------------------------------------|-----------------|----------|------------------------------|

| A8h                                     | 4               | Mode     | Mode Register <sup>(1)</sup> |

| ACh-FFh                                 |                 | Reserved |                              |

1. The Mode Register is required by the Linux programming model. It has no operational effect on the Host Controller function.

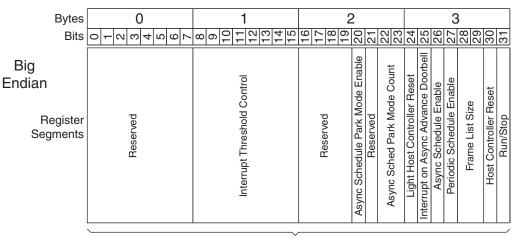

### USBCMD (USB Command Register)

The USB Command Register provides the user application with operational control and status. The register layout is shown in Figure 8 and described in Table 11.

#### **Big-endian/little-endian compatibility note:**

The USBCMD register must be accessed by software as a 4-byte (PLB word) entity.

USBCMD Register (32 bits)

DS734\_08\_053009

Figure 8: USBCMD Register Layout

| Bits  | Field Name                         | Default<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |