## Linux Netdev 10G

The FFSS-TE0950-Netdev-10G is an FPGA Full System Stack (FFSS), i.e. a **customizable FPGA design platform for Linux-based (non-accelerated) 10 GigE network connectivity**.

This FFSS combines an MLE optimized Linux network stack with Trenz Electronic's **TE0950** Evaluation Board featuring the **AMD Versal™ AI Edge VE2302**.

All key functionality is pre-integrated and pre-validated and ships as a **compilable FPGA design project** along **with an IP-Core license** from MLE.

## Use Cases

Application development of low data-rate networked systems<sup>1</sup> where **Your Linux application** transmits and/or receives data over a TCP/UDP/IPv4 network connected to 10 Gig Ethernet. Examples include:

- Camera sensor nodes

- Low-speed Robotics control

- IIoT Applications

Implement Your Linux userspace application and interface with a standard, open-source (non-accelerated) Linux networking stack via 10 GigE via the zQSFP of the TE0950 board.

## FPGA Full System Stack Key Features

- 150k LUTs total (approx. 140k LUTs free-for-use and 10k LUTs reserved by FFSS)

- Trenz TE0950 (AMD Versal™ AI Edge XCVE2302-1LSESFVA784 SoC with 8 GByte DDR4 SDRAM)

- 10 GigE subsystem, configured and wired to zQFSP via AMD PG292 and ARM A72 Linux

- “Unlimited” TCP/IP or UDP/IP sessions (not accelerated)

- Linux userspace scripts (use as design example)

- Linux OS (pre-installed root filesystem on SDCard)

- 1x RJ45 1 GigE LAN port (fully accessible from Linux)

## Ordering Information

| Model Name                                            | Part Number               | Description                                                                                |

|-------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------|

| TE0950 with 10G Linux Network Stack (Non-Accelerated) | FFSS-TE0950-Netdev-10G-01 | ARM A72 Linux 10 GigE NIC with a complete network stack (non-accelerated), based on TE0950 |

<sup>1</sup> This product is not designed or intended to be fail-safe, or for use in any application requiring fail-safe performance.

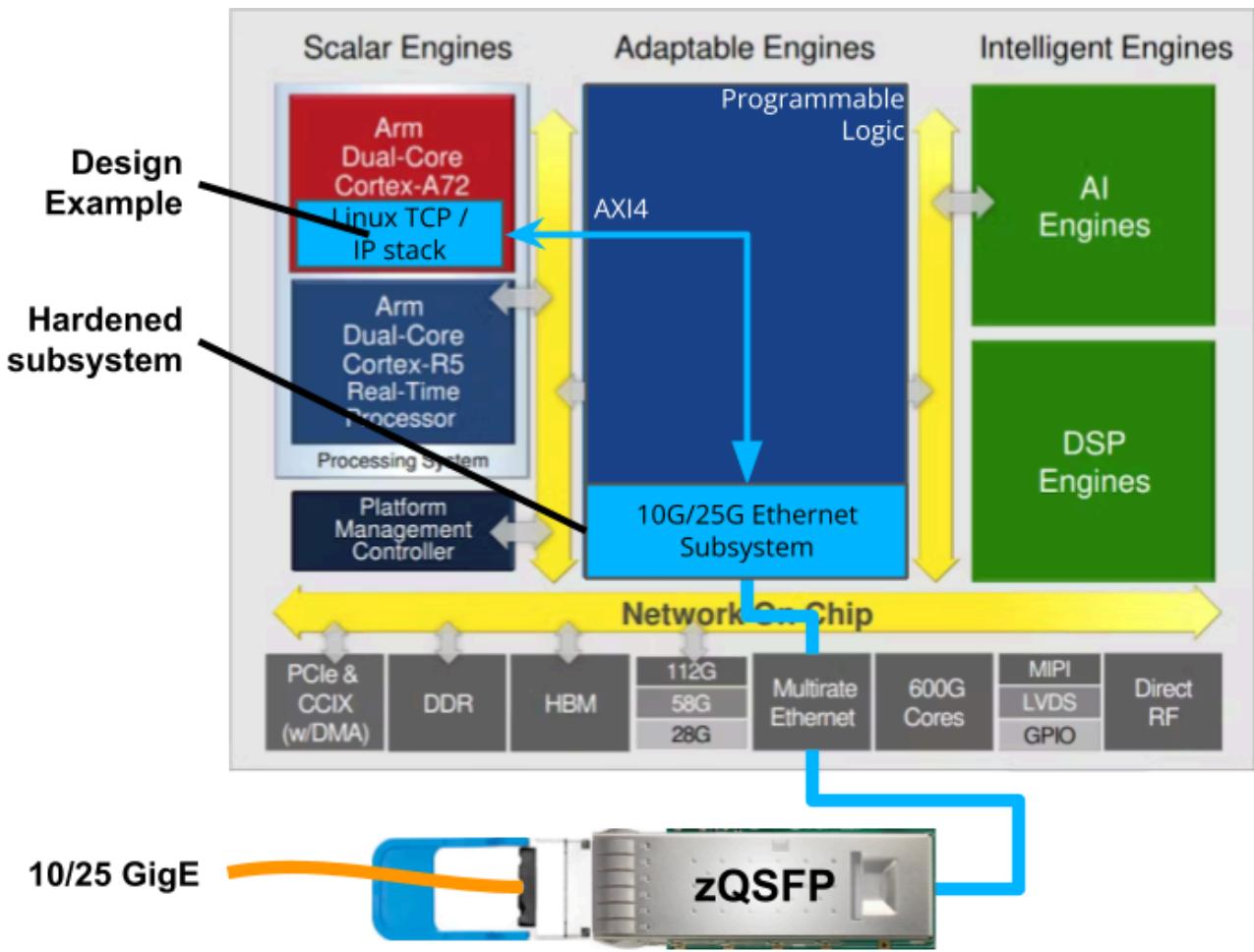

## FFSS Software and System-Level Block Diagram

This FFSS builds on top of the AMD Versal™ AI Edge XCVE2302 SoC<sup>2</sup> on the Trenz Electronic's TE0950 board<sup>3</sup> and runs open-source Linux. The 10 GigE subsystem is fully configured and wired to zQFSP via AMD PG292<sup>4</sup> and made available as a Linux network device (netdev) running on the ARM Cortex-A72 CPU.

Simply connect the TE0950 to your network (and, if wanted for debugging, a PC via UART) to immediately control and validate the 10G connection using the provided software. For custom FPGA development, you have almost the entire FPGA resources left to you.

<sup>2</sup> <https://www.amd.com/en/products/adaptive-socs-and-fpgas/versal/ai-edge-series.html>

<sup>3</sup> <https://www.trenz-electronic.de/en/AMD-Versal-AI-Edge-Evalboard-with-XCVE2302-device-8-GB-DDR4-SDRAM-15-x12-cm/TE0950-03-EGBE21C>

<sup>4</sup> <https://docs.amd.com/r/en-US/pg292-ethernet-1-10-25g>

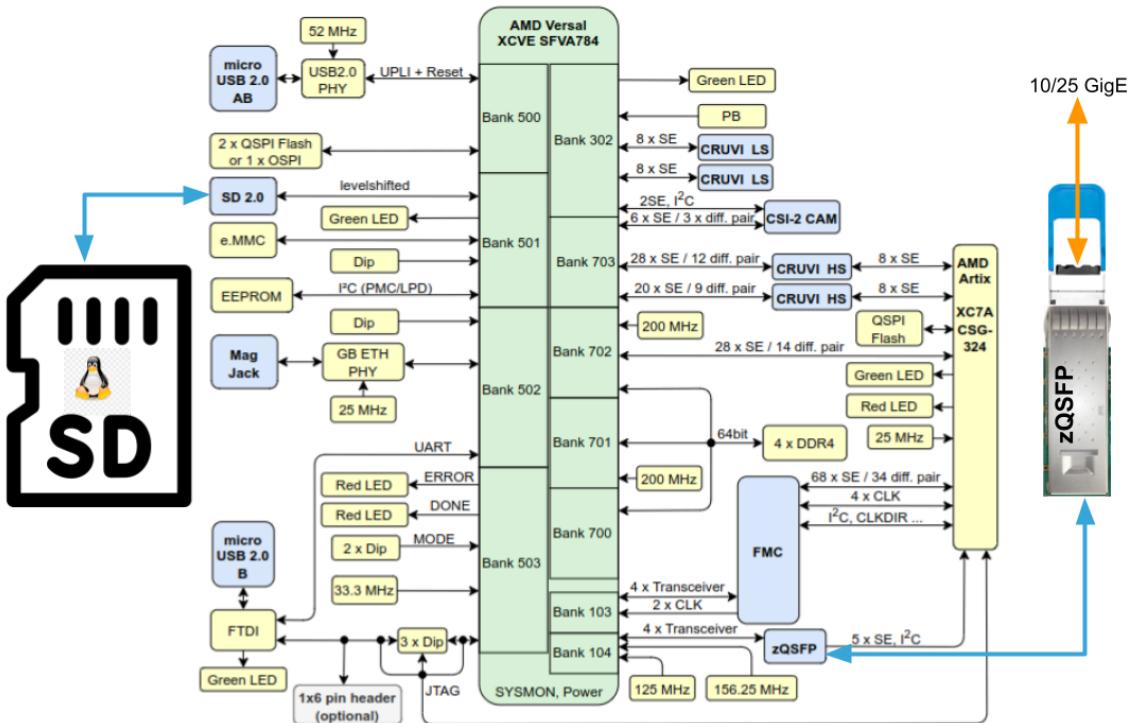

## FFSS Hardware Block Diagram

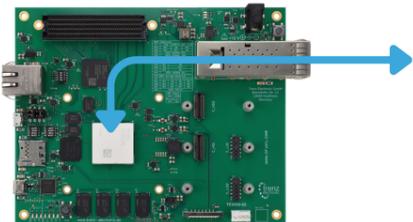

The hardware foundation for this FFSS is Trenz Electronic's TE0950 Evalboard featuring the AMD Versal™ AI Edge XCVE2302 SoC connected to many external I/Os.

- AMD Versal™ AI Edge XCVE2302-1LSESFVA784 device

- A784 package (pin compatible VE2202, VE2302, VM1102)

- AMD Artix™ 7 FPGA as configurable Levelshifter/MUX for FMC and other 3.3 V IOs

- 8 GByte DDR4 SDRAM

- 128 MByte QSPI Flash (primary boot option)

- MicroSD card (primary boot option)

- 32 GByte eMMC (secondary boot option)

- USB 2.0 Host/Device/OTG (type Micro A/B connector)

- Gigabit Ethernet RJ45

- zQSFP with 4 GTYP Transceiver

- 2 x CRUVI HS

- 2 x CRUVI LS

- CSI-2 connector (camera, 2 lane MIPI)

- FMC: 4 GTYP Transceiver

- Dimension: 150 mm x 120 mm

- More details at [Trenz TE0950 Wiki](#)

## Deliverables

- 1x Trenz TE0950 board

- 1x power adapter

- 1x CoolJag BUF-A4 Fansink

- 1x SD Card (to install root file system)

- Full FPGA System Stack Software, Firmware, Gateware including SD Card image with bitfile, Board Support Package, Linux, drivers (downloadable as binaries) and FPGA Design Project Archive (downloadable as compilable netlist)

- Single-project-use fully paid-up-for, perpetual commercial license for single unit (See [license details](#) below)

## Licensing

This FFSS comprises the following licenses from MLE. For more information regarding the legal license please refer to <https://missinglinkelectronics.com/de-license>

Proof-of-License (example)

Licensee: <YOU / YOUR COMPANY>

Product: "Netdev-10G-SPNL" (Netdev-10G Single-Project-Use Netlist License)

Project: <YOUR PROJECT NAME>

License Term: Perpetual

License Type: Fully-Paid-Up-For, Worldwide, Commercial Single-Project-Use License

Designated Equipment: AMD Versal™ AI Edge XCVE2302-1LSESFVA784 on TE0950

Designated Number of Instantiations: 1 (One)

Designated Number of Units: 1 (One)

Designated Site: <YOUR COMPANY ADDRESS>

## Contact Information

MLE USA: San Jose, CA

+1-408-475-1490

MLE Germany: Neu-Ulm

+49-7311-41149-0

Web: [www.missinglinkelectronics.com/](https://missinglinkelectronics.com/)

Email: [sales-web@mlecorp.com](mailto:sales-web@mlecorp.com)

Trenz Electronics

+49-5741-3200-0

Web: [www.trenz-electronic.de/en/](https://www.trenz-electronic.de/en/)

Email: [sales@trenz-electronic.de](mailto:sales@trenz-electronic.de)

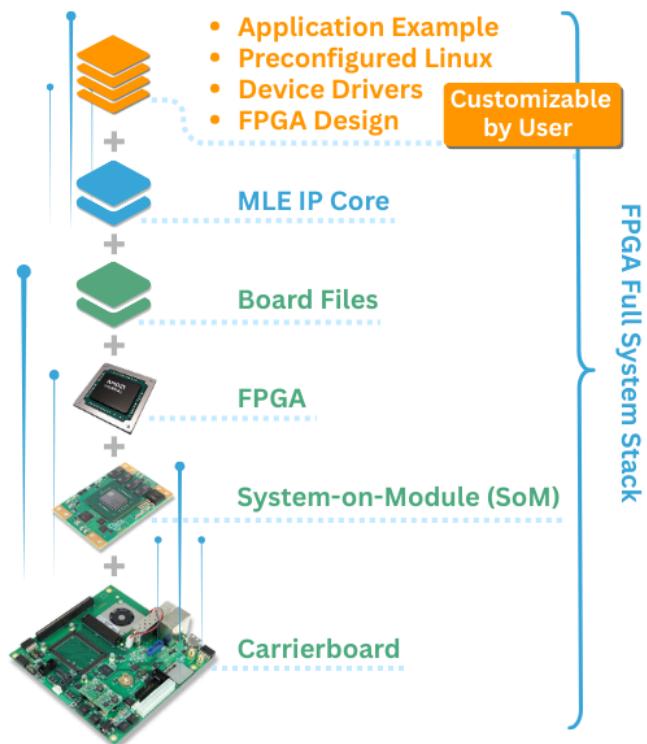

## FPGA Full System Stack (FFSS)

"When Wall Street wanted to program computers without having computer programmers, they invented the spreadsheet!" - This was our spirit when we came up with the FPGA Full System Stack: Make building FPGA-based systems easier for engineers without expert knowledge in FPGA design.

### Why FPGA Full System Stack?

For compute-intensive, time-critical applications in Automotive, Aerospace/Defence, Industrial/Scientific/Medical, FPGAs are often the choice. However, programming FPGAs, particularly those System-on-Chip (SoC) FPGA with embedded CPUs, has long been considered complex and risky.

Integrated and pre-validated building blocks of FPGA hardware and software subsystems, which we call "FPGA Full System Stack" can greatly de-risk development and accelerate new product initiatives.

### What makes up the FPGA Full System Stack?

Every FPGA Full System Stack comprises the following elements (top-down):

1. Application Example Subsystems which are customizable by users based on your applications

2. A Targeted Performance Subsystem, including one or more MLE IP-Cores

3. A Board Support Package, with a Linux Base System and Board Part Files

4. The FPGA device (such as the AMD VE2302, for example)

5. A SoM (such as the TE0955, for example)

6. A carrierboard (such as TEBF0955, for example)

Pre-integrating and testing this complex stack gives you, the implementer the advantages:

1. You can rely on a tested and verified subsystem implementation. The concept of re-use increases design productivity while sharing the FPGA subsystem development costs and risks over many users.

2. Pre-validated FPGA IPs and Subsystems make clever use of different FPGA resources to realize a cost/performance optimized domain-specific architecture. No need for reading long datasheets or making timing closure.

3. Operating system and application software is included in the form of kernel space device drivers, user-space programmer APIs, and sometimes even complete OS images, all nicely tuned for guaranteeing the overall system's reliability and performance.

## Other FPGA Full System Stacks

MLE and Trenz Electronics have been planning for many different FFSS to come. Our initial focus is on "embedded" platforms for performance networking and for performance storage / data acquisition based on AMD Versal AI Edge. Below are some examples.

If you are interested in other boards, other FPGA devices or other functionality, please contact us!

### Network Acceleration

**TCP/UDP/IP

10G**

**FFSS-TE0950-NPAP-10G**

Accelerated TCP/UDP/IP networking in PL up to 10 Gbps line-rate, based on TE0950

**MQNIC 10G**

**FFSS-TE0950-MQNIC-10G**

A configurable Multi-Queue FPGA NIC for 10 GigE in-network processing, based on TE0950

**Linux Netdev

10G**

**FFSS-TE0950-Netdev-10G**

ARM A72 Linux 10 GigE NIC with a complete network stack (non-accelerated), based on TE0950

**TCP/UDP/IP

25G**

**FFSS-TE0950-NPAP-25G**

Accelerated TCP/UDP/IP networking in PL up to 25 Gbps line-rate, based on TE0950

**MQNIC 25G**

**FFSS-TE0950-MQNIC-25G**

A configurable Multi-Queue FPGA NIC for 25 GigE in-network processing, based on TE0950

**Linux Netdev

25G**

**FFSS-TE0950-Netdev-25G**

ARM A72 Linux 25 GigE NIC with a complete network stack (non-accelerated), based on TE0950

### Storage Acceleration

**NVMePS**

**FFSS-TE0950-NVMePS**

Data read/write onto a Linux-connected NVMe SSD using Linux file system, based on TE0950

**NVMePL x1**

**FFSS-TE0950-NVMePL-x1**

Accelerated NVMe data streaming with 1 lane in PL, based on TE0950

**NVMePL x4**

**FFSS-TE0950-NVMePL-x4**

Accelerated NVMe data streaming with 4 lanes in PL, based on TE0950