News

MLE continues to work with a wide range of partners to develop advanced FPGA-based networking and storage applications, as well as to share our experience and latest research results in seminars as well as webinars. Here we share our latest news and events.

MLE Presents “Light Rabbit: Implementing a White Rabbit node on COTS AMD development boards without relying on external VCXOs” at The 13th White Rabbit Workshop

The 13th White Rabbit Workshop will be held March 21-22 at CERN in Geneva, Switzerland. There, MLE will present “Light Rabbit: Implementing a White Rabbit node on COTS AMD development…

MLE Updates TCP/UDP/IP Network Protocol Accelerator Platform

MLE has released an update, Version 2.3.3., of its Network Protocol Acceleration Platform (NPAP). This update is fixing minor issues with AXI4 bus scheduler fairness, IP Core packaging for AMD/Xilinx…

Shift-Left Your FPGA Design Project with FPGA Full System Stacks from Trenz Electronic and MLE

Visit us at Embedded World 2024! The Embedded World 2024 tradeshow will be held April 9-11 in Nuremberg, Germany. Here, partners Trenz Electronic and MLE will present solutions for you…

MLE Presents “Architecture and Performance of Integrated High-speed and Versatile Embedded Networking” at Embedded World 2024

The Embedded World Conference 2024 will be held April 9-11 in Nuremberg, Germany. There, MLE will present “Architecture and Performance of Integrated High-speed and Versatile Embedded Networking.” These days high-performance…

MLE Presents “FPGA Based High Speed Recording – Do’s and Don’t’s of Building a 400GBit/s Data Recorder” at Embedded World 2024

The Embedded World Conference 2024 will be held April 9-11 in Nuremberg, Germany. There, MLE will present “FPGA Based High Speed Recording – Do’s and Don’t’s of Building a 400GBit/s…

MLE Presents “TCP/IP for Real-Time Embedded Systems: The Good, the Bad and the Ugly” at Embedded World 2024

The Embedded World Conference 2024 will be held April 9-11 in Nuremberg, Germany. There, MLE will present “TCP/IP for Real-Time Embedded Systems: The Good, the Bad and the Ugly.” Embedded…

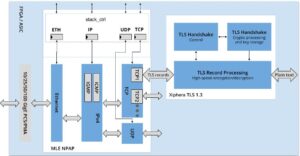

Xiphera and Missing Link Electronics Announce a Partnership for Encrypted Network Accelerator Solutions (ENAS)

With the new Encrypted Network Accelerator Solutions brought to the market, Xiphera and MLE offer a cryptographically secure and reliable connection between devices over TCP/IP. Xiphera, Ltd, designing hardware-based security…

MLE Participates at AMD/Xilinx Security Working Group 2023

The AMD-Xilinx Security Working Group takes place face-to-face in Munich, Germany, from December 5-6, 2023. Presentations include the latest security features in Versal ACAP and updates for the product roadmap.…

MLE Co-Exhibits with Prodesign at Super Computing Conference 2023

Partner ProDesign and MLE will showcase the latest FPGA-based High-Performance Compute solutions at Super Computing Conference SC23. To address the acceleration needs of Disaggregated Computational Storage or At-Speed In-Network Processing,…

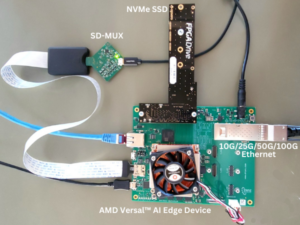

MLE and Trenz Verify the AMD/Xilinx Versal™ AI Edge Device and Accelerate Networking and Storage with 10G/25G/50G/100G TCP/IP Core

MLE and Trenz Electronic, both Premier Members of the AMD Adaptive Computing Partner Program, have collaborated and worked on Trenz’s new TE0950 AMD/Xilinx Versal™ AI Edge Evalboard to provide an…