News

MLE continues to work with a wide range of partners to develop advanced FPGA-based networking and storage applications, as well as to share our experience and latest research results in seminars as well as webinars. Here we share our latest news and events.

MLE Auto/RPS and Auto/TSN For In-Vehicle Networking Have Been Featured By The BMFTR MANNHEIM CeCaS Project For Central Car Server

Modern Software-Defined Vehicle (SDV) architectures are pushing automotive in-vehicle networks towards more bandwidth and lower, guaranteed transport latency as cars are expected to be an integral part of a broader…

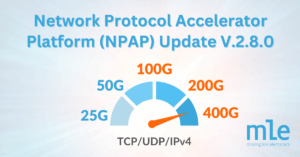

MLE Releases Network Protocol Accelerator Platform (NPAP) Version 2.8.0

MLE has released Version 2.8.0 of its Network Protocol Accelerator Platform (NPAP) along with new versions for Evaluation Reference Designs, including support for AMD’s cost-optimized Artix Ultrascale+ device family. NPAP is…

MLE Showcases NVMe Fast FPGA RAID – The Newest Storage Acceleration Technology at AMD 2025 EMEA Signal Processing Working Group

At AMD’s 2025 EMEA Signal Processing Working Group on Oct. 29-31 at AMD Dublin, Ireland, MLE presented the newest storage acceleration technology: the NVMe Fast FPGA RAID (FFRAID). With MLE…

MLE presents “From Software to Silicon: Accelerating Automotive In-Vehicle Network Protocols for Zonal Architectures” at the “Driving the Future Symposium”

The Driving the Future Symposium will be held on October 8-9 in Munich, Germany. There, MLE will present “From Software to Silicon: Accelerating Automotive In-Vehicle Network Protocols for Zonal Architectures.”…

MLE and CODESYS Collaborate on Converged OT/IT Networks for Virtualized PLCs

MLE Robo/TSN converges OT and IT networks and, thereby, enables virtualized PLCs in a Factory Cloud via secure “tunnels” to transport existing OT fieldbus protocols over standard IEEE TSN Ethernet.…

MLE Joins CC-Link Partner Association (CLPA)

CC-Link, short for Control and Communications Link, is a widely adopted fieldbus system used in industrial automation. The CC-Link Partner Association (CLPA), based in Japan, is dedicated to promoting the…

Lattice Semiconductor and Missing Link Electronics Become Partners to Accelerate FPGA Design Projects

Missing Link Electronics (MLE) is now a partner of Lattice Semiconductor, providing a range of pre-validated FPGA IP cores and licensable system stacks optimized for Lattice FPGAs. This collaboration is…

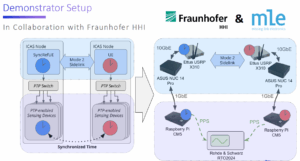

MLE Presents “Enabling PTP-based Time-of-Day Synchronization via 5G Sidelink” at Berlin 6G Conference 2025

Berlin 6G Conference is the annual networking event of the German 6G Program, organized by the 6G Platform Germany, taking place at the Berlin Congress Center (BCC) from July 1-3,…

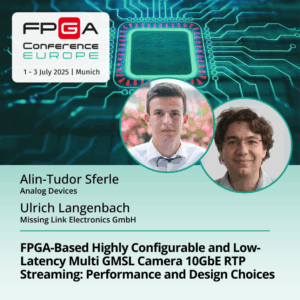

MLE and Analog Devices Jointly Present “FPGA-Based Highly Configurable and Low-Latency Multi GMSL Camera 10GbE RTP Streaming: Performance and Design Choices” at FPGA Conference 2025

The FPGA Conference Europe 2025 will be held July 1-3 in Munich, Germany. There, Partner Analog Devices and MLE will together present “FPGA-Based Highly Configurable and Low-Latency Multi GMSL Camera…

MLE Presents “In-Vehicle Network – Automotive Zone-based Architecture with Time Sensitive Network – Auto/TSN” at FPGA Conference 2025

The FPGA Conference Europe 2025 will be held July 1-3 in Munich, Germany. There, MLE will present “In-Vehicle Network – Automotive Zone-based Architecture with Time Sensitive Network – Auto/TSN.” Automotive…