Presentation at PCI-SIG Developers Conference 2019

MLE presents “Sensor Fusion and Data-in-Motion Processing for Autonomous Vehicles” at the PCI-SIG Developers Conference 2019.

MLE presents “Sensor Fusion and Data-in-Motion Processing for Autonomous Vehicles” at the PCI-SIG Developers Conference 2019.

Xilinx features Missing Link Electronics as a Premier Partner offering IP, Design Services and Software for key markets Aerospace & Defense, Automotive, Data Center, Industrial, Wired Communications, Wireless Communication.

Solutions and services from Missing Link Electronics include Security (OP-TEE), crypto subsystems, connectivity (PCIe, Ethernet, USB, SATA, NVMe) IP integration, camera/lidar/radar data acquisition and aggregation processing, Functional Safety, TCP/UDP/IP Full Accelerators, Key-Value-Store Accelerators, Digital Signal Processing IP (PAM/QAM Multi-format mapper, OFDM transmitter, WOLA channelizer, Adaptive time-domain equalizer, FFT), PetaLinux Design Service.

TUE FEB 26 – THU FEB 28 – Exhibition Nuremberg – live demo at the Xilinx Booth

Booth 3A-235: Zync UltraScale+ RFPSoC – Software Defined Radio

This Software Defined Radio demonstration showcases the Zynq® UltraScale+™ RDSoC multi-giga-sample RF data converters, and soft-decision forward error correction (SD-FEC), integrated into a SoC architecture. Complete with an ARM® Cortex™-A53 processing subsystem, UltraScale+ programmable logic, and the highest signal processing bandwith in a Zynq UltraScale+ device, this family provides a comprehensive FR signal chain for wireless, cable access, test & measurement, early warning / radar, and other high performance FR applications.

WED JAN 4 2019

Responding to needs for additional engineering lab space for customer system hardware setup and integration testing, Missing Link Electronics expands office space in Neu-Ulm, Germany.

TUE FEB 26 – THU FEB 28 – Exhibition Nuremberg

In addition to our technical presentations at Embedded World 2019, MLE’s FPGA experts will be available at Booth 3A-430 in Hall 3A. More information coming soon.

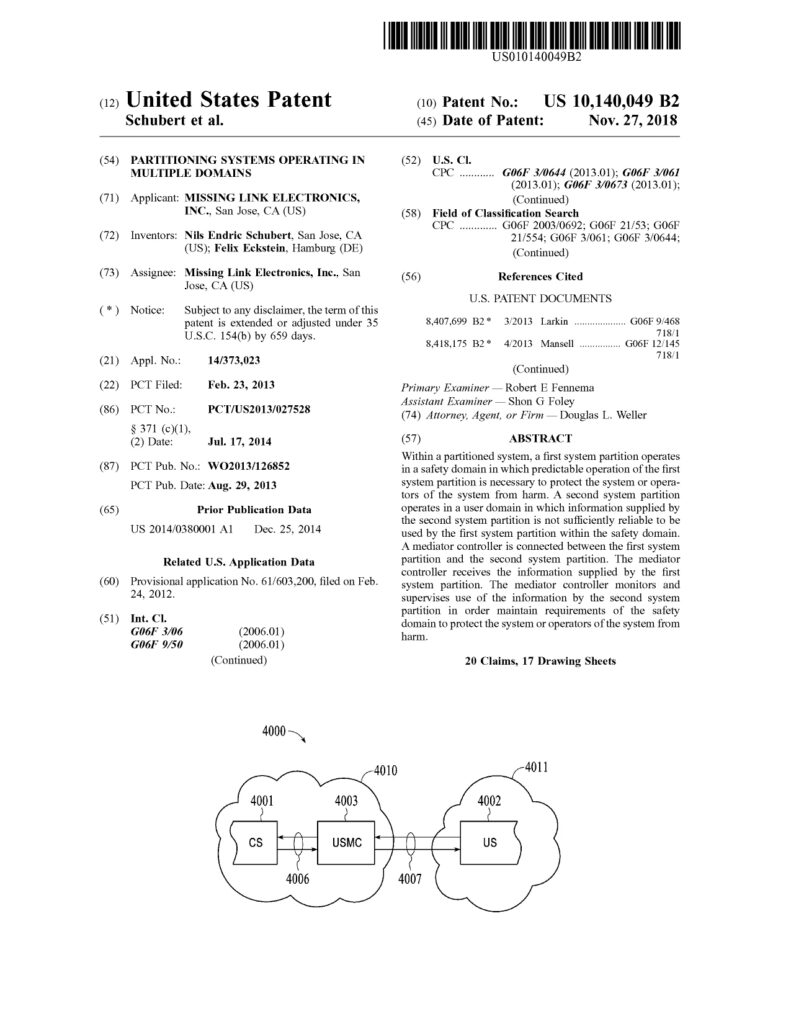

In the area of Functional Safety for Reconfigurable Systems, Missing Link Electronics has been awarded US Patent 10,140,049. This patent is titled “Partitioning Systems Operation in Multiple Domains”.

WED FEB 27, 2019 – Embedded World Conference 2019 at MCC Ost:

MLE FPGA experts will present at Embedded World Conference: Session 5.4 “Power Supply”, MLEs’ Director of Applications Andreas Schuler presents “OP-TEE – An Intro to a Trusted Execution Environment“, beginning: 4:00 PM. Cedrik Bock, Design Engineer (M-Sc. EE) at MLE, presents “System-Level Modeling of Heterogeneous Compute Architectures for NVMExpress Protocol Acceleration” at Conference Session 10.2 II SoC II EDA II, beginning 4:00 PM.

![]() OpenPOWER Summit Europe 2018 – Amsterdam RAI Exhibition and Convention Center

OpenPOWER Summit Europe 2018 – Amsterdam RAI Exhibition and Convention Center

The presentation is titled “Network Protocol Acceleration with CAPI SNAP” and will show first results of a collaboration between Alpha-Data, Dr. Andrew McCormick, and MLE, Dr. Endric Schubert, on OpenCAPI SNAP FPGA acceleration for IBM OpenPOWER Power 8 and Power 9.

![]() XILINX DEVELOPER FORUM, 1.+ 2.October 2018 – Fairmont, San Jose

XILINX DEVELOPER FORUM, 1.+ 2.October 2018 – Fairmont, San Jose

MLE will showcase its solutions and services at the XDF. Andreas Schuler, Director Applications at MLE, presents OP-TEE for Zynq UltraScale+ MPSoC at the Xilinx Security Design Workshop which is co-located with XDF. View Agenda >>