Technical Publications

MLE has been invited to numerous international seminars and webinars to share our experience in FPGA development using advanced PCI Express, TCP/UDP/IP stacks, and low-latency IP-core technologies for network and storage acceleration. Here we share the full technical articles and slides of the up-to-date presentations.

Cost-Optimizing High-Accuracy Precision Time Protocol

Presentation at Automotive Ethernet Congress 2026, Munich, Germany, March 24-26, 2026 ADAS with coherent, multi-static, digital RADAR benefits from automotive Ethernet but demands more precise time synchronization and clock-phase recovery.…

From Software to Silicon: Accelerating Automotive In-Vehicle Network Protocols for Zonal Architectures

Presentation at Driving the Future Symposium 2025, Munich, Germany, Oct. 8-9, 2025 Modern Software-Defined Vehicle (SDV) architectures are pushing automotive in-vehicle networks towards more bandwidth and lower, guaranteed transport latency.…

Real-time Virtualized Motion Control for Industrial Automation (Echtzeitanwendungen für Motion und Robotik mit virtuellen Steuerungen)

Traditional PLCs have long been the backbone of industrial automation, but they come with significant limitations: high hardware costs, rigid scalability, complex maintenance, and vendor lock-in. Updating systems or adding…

Overcoming The Real-Time Hurdle (Die Echtzeithürde überwinden)

To meet the hard real-time requirements of modern motion control systems, MLE Robo/TSN uses hardware acceleration to implement secure “tunnels” which transport existing OT fieldbus protocols over standard IEEE TSN…

Enabling PTP-based Time-of-Day Synchronization via 5G Sidelink

Presentation at 6G Conference 2025, Berlin, Germany, July 3rd, 2025 GNSS is widely used for positioning and synchronization—particularly in applications, such as vehicles and drones, where merging recorded radar data…

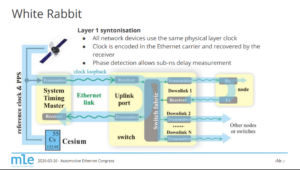

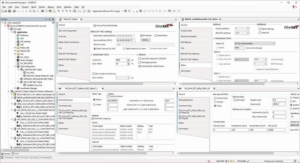

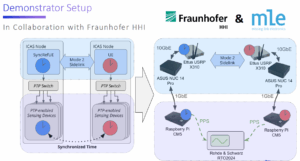

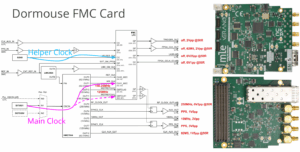

White Rabbit at MLE – Updates on Dormouse FMC Card, Light Rabbit and Further Contributions

Presentation at the 14th White Rabbit Workshop 2025 at CERN in Geneva, Switzerland, Jun 25-26, 2025 White Rabbit is a technology that allows to synchronize networked devices or endpoints tens…

FPGA-Based Highly Configurable and Low-Latency Multi GMSL Camera 10GbE RTP Streaming: Performance and Design Choices

Presentation at FPGA Conference 2025, Munich, Germany, July 3rd, 2025 In the decade of high-performance networking and computing, FPGAs have arisen as a promising and highly convenient solution, offering flexibility,…

In-Vehicle Network – Automotive Zone-based Architecture with Time Sensitive Network – Auto/TSN

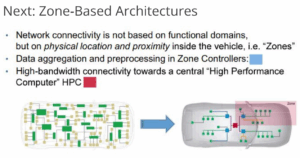

Presentation at FPGA Conference 2025, Munich, Germany, July 3rd, 2025 Automotive architectures are transforming: while more and more sensors become integrated in vehicles, the automotive industry is looking for ways…

Zonal/SDV Architecture Exploration: From Whiteboard to Vehicle Demo in 9 Months

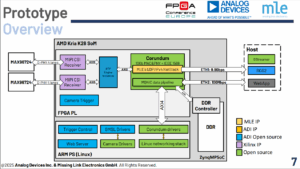

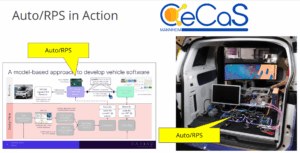

Presentation at AMD Technology Day, Gothenburg, Sweden, June 4th, 2025 For the AMD Technology Day in Gothenburg, Sweden, MLE presented an automotive rapid prototyping system for architecture exploration and development…

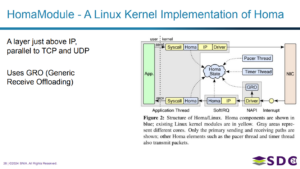

Complementing TCP with Homa, Stanford’s Reliable, Rapid Request-Response Protocol

Presentation at SNIA Storage Developers Conference, Santa Clara, CA, Sept. 16-18, 2024 At SDC 2023 last year, we presented Homa, a new datacenter protocol invented by John Ousterhout at Stanford…