FPGA-Based Recording to NVMe SSDs

MLE publishes Technical Brief MLE-TB20201012 “Sustained, High-Speed Data Recording with NVMe SSDs” discussing read/write performance aspects of various NVMe SSDs.

MLE publishes Technical Brief MLE-TB20201012 “Sustained, High-Speed Data Recording with NVMe SSDs” discussing read/write performance aspects of various NVMe SSDs.

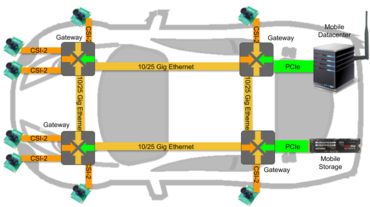

MLE presents "PCIe-over-TCP-over-TSN-over10/25GigE" at the 4th Workshop "Programmable Processing for the Autonomous / Connected Vehicle".

MLE presents "PCIe-over-TCP-over-TSN-over10/25GigE" at the 4th Workshop "Programmable Processing for the Autonomous / Connected Vehicle".

This workshop was hosted by Technische Hochschule Ulm (THU) on September 24, 2020.

Click here to see the slides of the presentation.

MLE updates NVMe Streamer a so-called Full Accelerator NVMe host subsystem integrated into Xilinx FPGAs. This update covers new NVMe SSD features such as changes in default page size and performance enhancements to support maximum bandwidth for modern PCIe Gen3 x4 m.2 SSD.

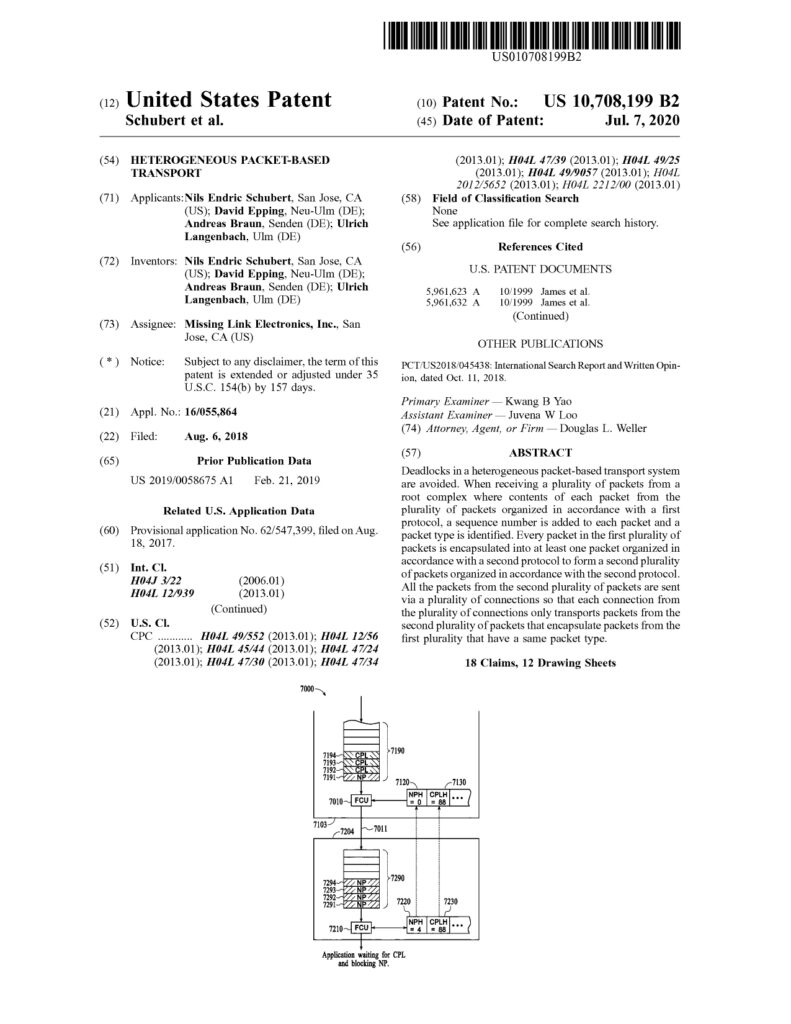

Missing Link Electronics has been awarded US Patent 10,708,199 on Heterogeneous Packet-Based Transport which covers aspects of tunneling packets such as PCI Express (PCIe) Transaction-Layer Packets (TLP) over reliable TCP/IP over 1/10/25/50/100G Ethernet. This extends the range of PCIe and enables building distributed systems based on PCIe.

MLE and Xilinx, for the 4th time, will co-sponsor the Workshop "Programmable Processing for the Autonomous / Connected Vehicle".

MLE and Xilinx, for the 4th time, will co-sponsor the Workshop "Programmable Processing for the Autonomous / Connected Vehicle".

This workshop is organized by Technische Hochschule Ulm (THU) and will be held "100% online" on September 24, 2020.

Click here to see the Call-for-Paper. Deadline is July 17, 2020.

Missing Link Electronics (MLE) has released update V1.4.9 for the network acceleration technology from German Fraunhofer Heinrich-Hertz-Institute. Changes include various fixes for corner cases and to enhance support for the Xilinx 10G/25G PCS/PMA subsystem. This brings full TCP/UDP/IP connectivity for 10/25/40/50 Gigabit Ethernet to FPGAs by offloading protocol processing into programmable logic.

Missing Link Electronics (MLE) has partnered with Trenz Electronic to deliver FPGA-based turnkey solutions integrating FPGA and SoC modules manufactured by Trenz and IP Cores and Subsystems from MLE.

![]() The Xilinx Alliance Partner Program, a worldwide ecosystem of qualified companies who offer Acceleration solutions, IP cores, Design Services, and Board development & production, features Missing Link Electronics professional services for Security. The services are built on-top of a strong foundation using Xilinx Zynq UltraScale+ MPSoC and Xilinx Zynq UltraScale+ RFSoC Hardware Root-of-Trust and open source ARM Secure OP-TEE.

The Xilinx Alliance Partner Program, a worldwide ecosystem of qualified companies who offer Acceleration solutions, IP cores, Design Services, and Board development & production, features Missing Link Electronics professional services for Security. The services are built on-top of a strong foundation using Xilinx Zynq UltraScale+ MPSoC and Xilinx Zynq UltraScale+ RFSoC Hardware Root-of-Trust and open source ARM Secure OP-TEE.

MLE will support researchers in using the Intel Programmable Accelerator Cards (PAC) D5005 installed in the new High-Performance Cluster JUSTUS 2 at Ulm University in Germany. As an Intel FPGA Design Solutions Partner MLE has been given access to FPGA design tools and design methodologies including Intel oneAPI Data Parallel C++ and and will actively work with the KIZ at Ulm University so researches see maximum results from FPGA acceleration.

MLE will support researchers in using the Intel Programmable Accelerator Cards (PAC) D5005 installed in the new High-Performance Cluster JUSTUS 2 at Ulm University in Germany. As an Intel FPGA Design Solutions Partner MLE has been given access to FPGA design tools and design methodologies including Intel oneAPI Data Parallel C++ and and will actively work with the KIZ at Ulm University so researches see maximum results from FPGA acceleration.