MLE Presents “Cost-Optimizing High-Accuracy Precision Time Protocol” at Automotive Ethernet Congress 2026

The Automotive Ethernet Congress will be held on March 24-26, 2026 in Munich, Germany. There, MLE will present “Cost-Optimizing High-Accuracy Precision Time Protocol.”

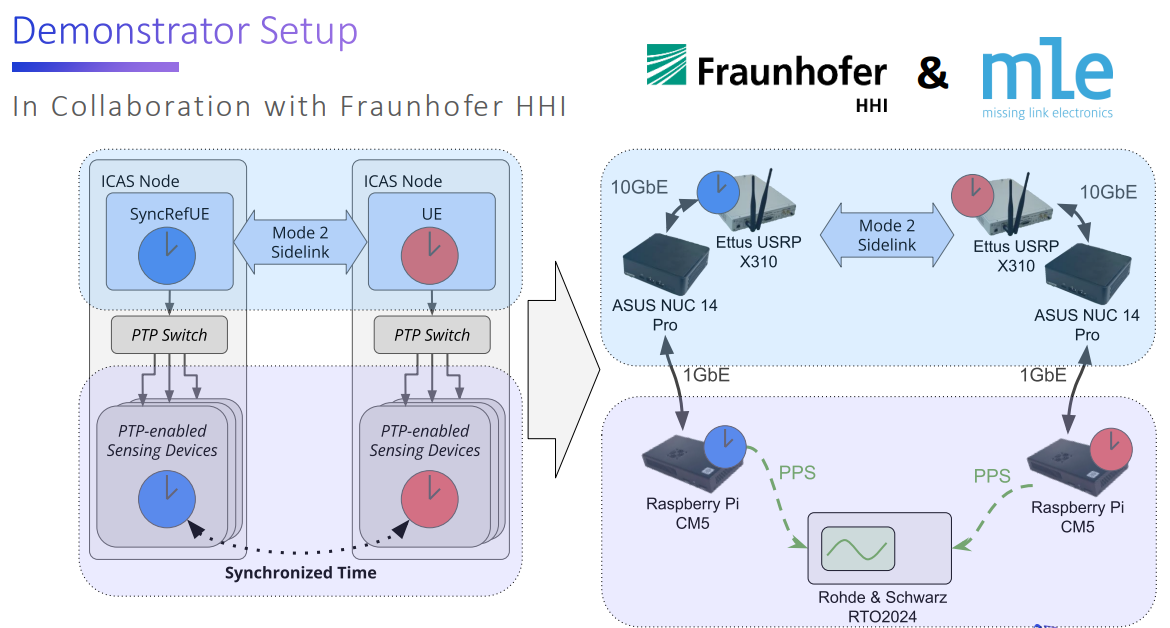

ADAS with coherent, multi-static, digital RADAR benefits from automotive Ethernet but demands more precise time synchronization and clock-phase recovery.

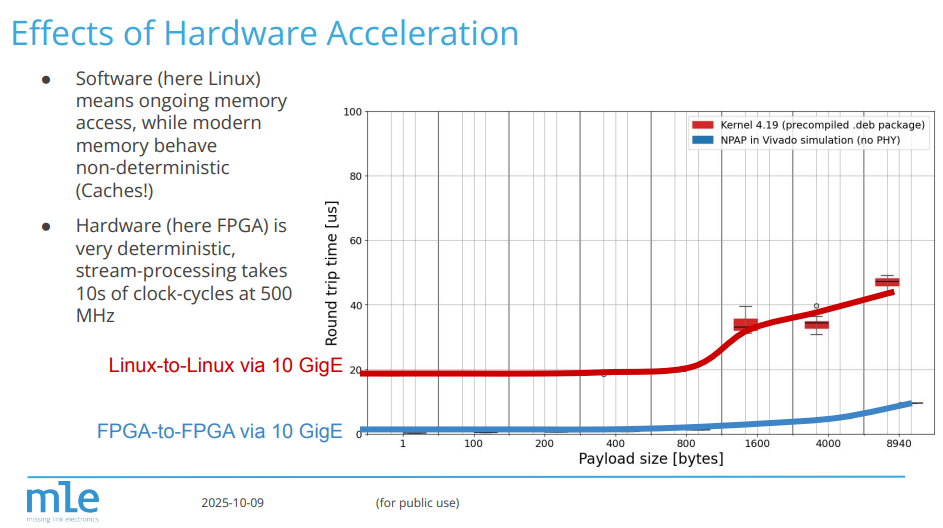

First we give an overview over time synchronization: NTP, GNSS, PTP, with a deep-dive into the PTP (including hardware assisted time stamping for accuracy and precision around 10 nanoseconds), down to the high-accuracy Precision Time Protocol IEEE 1588-2019 (PTP-HA) developed by CERN’s White Rabbit group for large scale physics experiments in need of < 1 ns accuracy and < 100 ps precision.

Second we present “Light Rabbit”, a collaboration between CERN and MLE. Using modern on-chip PLL for phase-shifting we complement (or replace) expensive VCXOs and trade-off BoM cost vs. minor loss of accuracy.

We close with experimental results for an OFDM RADAR network where Ethernet transports status, control and sensor data and distributes time (i.e. trigger), frequency and phase information to steer oscillators in the RF subsystem.

Date: Thursday March 26, 2026

Session 6 – TSN (starts at 10:30am CEST)

Location: Science Congress Center Munich, Germany

Join us at Automotive Ethernet Congress 2026 to learn more about the “Light Rabbit” solution to complement White Rabbit technology for high-accuracy time synchronization of digital radar networks!