Zone-Based Automotive Backbones Tunneling PCIe

Missing Link Electronics (MLE) announced today that they are partnering with Fraunhofer Heinrich-Hertz-Institute (HHI) and Fraunhofer Institute for Photonic Microsystems (IPMS) on ultra-reliable, deterministic low-latency transports for automotive networks tunneling PCI Express® (PCIe®) architecture.

Missing Link Electronics (MLE) announced today that they are partnering with Fraunhofer Heinrich-Hertz-Institute (HHI) and Fraunhofer Institute for Photonic Microsystems (IPMS) on ultra-reliable, deterministic low-latency transports for automotive networks tunneling PCI Express® (PCIe®) architecture.

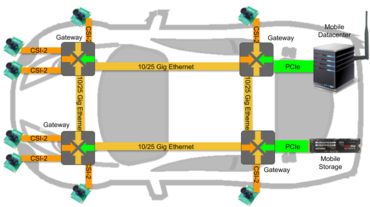

The need for more safe and eco-friendly vehicles drives automotive connectivity towards so-called Zone-Based Architectures. Inside those so-called Zone Gateways PCIe technology provides the connectivity between multiple System-on-Chip (SoC), CPUs, GPUs, and FPGAs for scalable performance. Within the automotive network, multiple Zone Gateways connect with each other via the emerging IEEE standards “Time Sensitive Networking” (TSN).

Today, Fraunhofer and MLE can provide a working proof-of-concept in form of a digital circuit & system stack which encapsulates and decapsulates PCIe packets (and other protocols) over real-time automotive TSN Ethernet and which scales up to 100 Gbps.

“When we started working on network protocol acceleration in 2010 we looked at future connectivity needs for systems-of-systems such as ships and cars”, states Ulrich Langenbach, formerly with Fraunhofer HHI and now Director Engineering at MLE. “Therefore, our approach does address key topology requirements for modern vehicles which is reliable and cost-efficient PCIe long-range, support for NVMe SSD storage, as well as CPU-to-CPU communication via PCIe Non-Transparent Bridges (NTB)”.

“Our approach of closely adhering to the OSI Layers makes our TSN Switched-Endpoint very interoperable with different Ethernet PHY solutions”, says Marcus Pietzsch, Group Leader IP Cores and ASIC Design at IPMS and emphasizes: “This is vital as the standards and commercial offerings for TSN and for automotive Ethernet are still very fluid!”

“PCI-SIG’s mission is to bring together developers seeking innovation and product compliance around current and future PCIe specifications,” said PCI-SIG President Al Yanes. “The purpose of PCI-SIG’s Automotive Work Group is to facilitate the discussion of PCIe technology in the automotive ecosystem with member companies like MLE.”