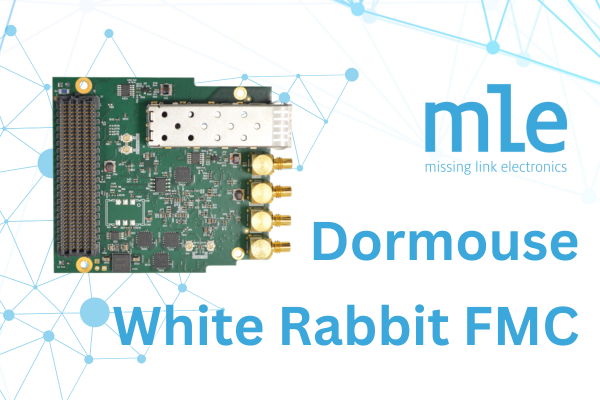

MLE Ships 1st Dormouse White Rabbit FPGA FMC: Achieving PTP v2.1 at Sub-Nanosecond Accuracy

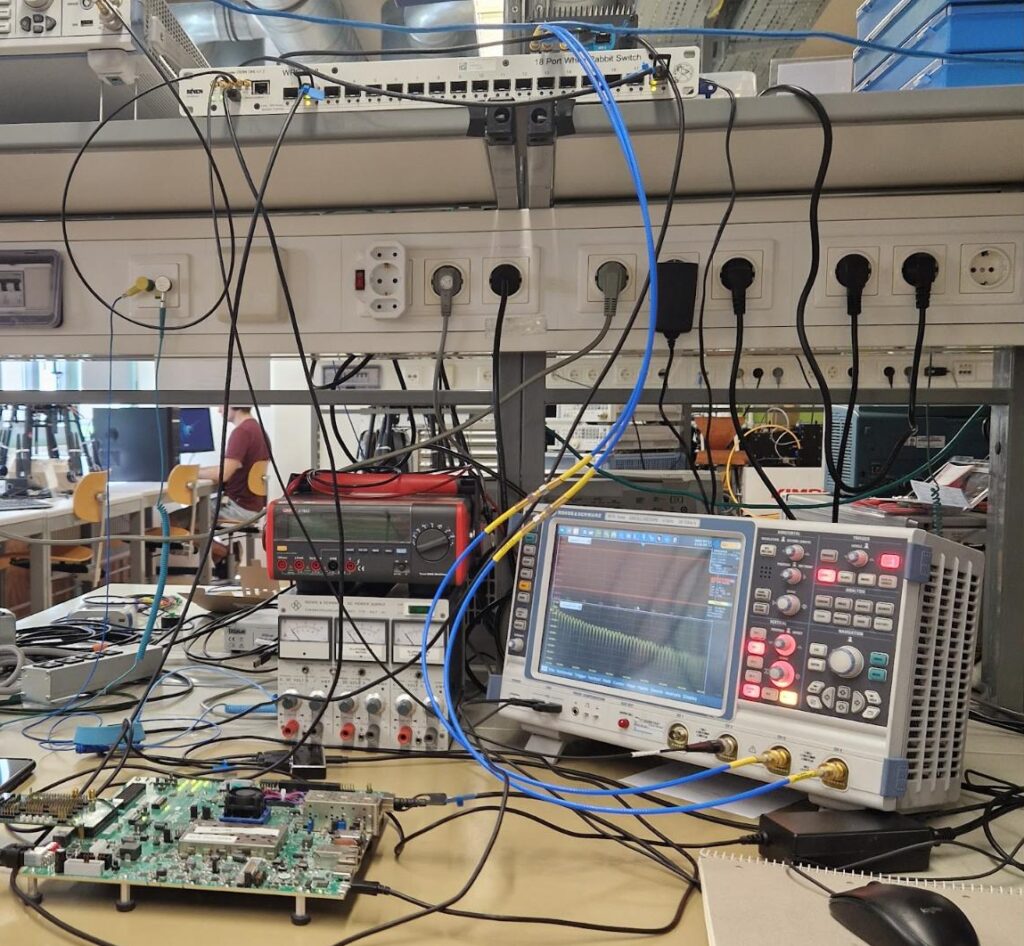

MLE is shipping to the first customers the Dormouse White Rabbit FPGA Mezzanine Card (FMC), specifically designed to implement White Rabbit technology for highly accurate time and frequency distribution Ethernet-based networks.

The Dormouse White Rabbit FPGA FMC features tunable oscillators that are required to deploy and operate White Rabbit, an open-source FPGA-based implementation of Precision Time Protocol 2.1 (PTP v2.1). With the Dormouse White Rabbit FPGA FMC, White Rabbit implementation can achieve sub-nanosecond accuracy of the PTP v2.1 high-accuracy profile, making it an ideal solution for building a time and frequency distribution network for applications like data center, radar, neutrino telescope, automotive, or control systems.

The Dormouse White Rabbit FPGA FMC provides capabilities to generate LF and RF reference clocks derived from a White Rabbit network. For these tasks a high performance OCXO (DOT050V), two programmable and tunable oscillators (SiT3521, Si549) and a flexible PLL (HMC7044) are available for use on the card.

In addition to the clocking infrastructure, an SFP+ interface provides 1 GbE / White Rabbit connectivity, which enables boards that do not provide an SFP+ interface.

Features of White Rabbit High-Accuracy Time Synchronization:

- Compatible with:

- Zynq UltraScale+ MPSoC ZCU102 Evaluation Kit

- Zynq UltraScale+ MPSoC ZCU106 Evaluation Kit

- Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit

- Other AMD/Xilinx FPGA Development Boards

- IEEE 1588-2019 PTP V2.1

- Typical Accuracy ~ 1 Nanosecond

- ANSI/VITA 57.1 FPGA Mezzanine Card Form Factor

- SFP+ 10 GigE Connector

- Connor-Winfield DOT050V OCXO

- SiTime Tunable Oscillators SiT3521/Si549

- Analog Devices Flexible PLL HMC7044

- TI Wideband Synthesizer LMX2594

- Clock Rates (default): 10 MHz, 62.5 MHz, 125 MHz, 250 MHz

- Designed in Accordance to The CERN Open Hardware License (OHL)

The MLE Dormouse White Rabbit FMC is now available on our partner Trenz’s online shop.

About White Rabbit Project

The White Rabbit Project is a multi-laboratory, multi-company and multinational collaboration to develop new technology that provides a versatile solution for control and data acquisition systems. The White Rabbit Network is based on existing IEEE standards while extending these standards in a backward-compatible way if needed to meet CERN‘s requirement.